Nanosecond grade digital synchronizer based on FPGA high-speed serial bus

A high-speed serial bus, synchronous machine technology, applied in synchronous transmitters, synchronous devices, digital transmission systems, etc., can solve the problems of narrow delay range, cumbersome methods, large area, etc., to achieve a wide delay range and reduce volume , the effect of small size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to clearly understand the technical solution of the present invention, its detailed structure will be presented in the following description. Obviously, the implementation of the embodiments of the invention is not limited to specific details familiar to those skilled in the art. The preferred embodiments of the present invention are described in detail below, and there may be other implementations besides those described in detail.

[0027] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

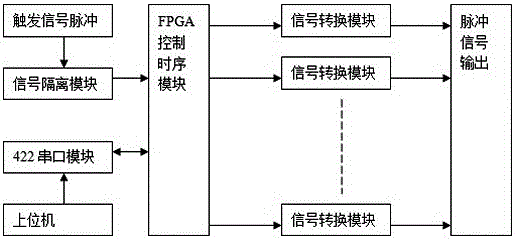

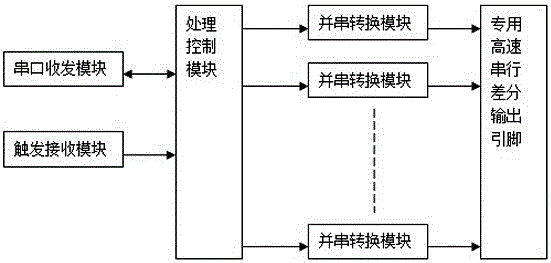

[0028] The present invention is a nanosecond-level digital synchronization machine based on FPGA high-speed serial bus, which is provided for high-precision synchronization and pulse width modulation within a wide delay range of multiple devices. figure 1 , the digital synchronous machine includes a trigger signal module, a signal isolation module, an FPGA control timing module, a signal conversi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com