Novel P<+> sidewall non-junction field effect transistor

A junction field effect and transistor technology, which is applied in the field of new P+ sidewall junctionless field effect transistors, can solve the problems of limited leakage current control of junctionless devices, insufficient leakage current control ability, and inability to form greater control capabilities.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be described in detail below in conjunction with the accompanying drawings.

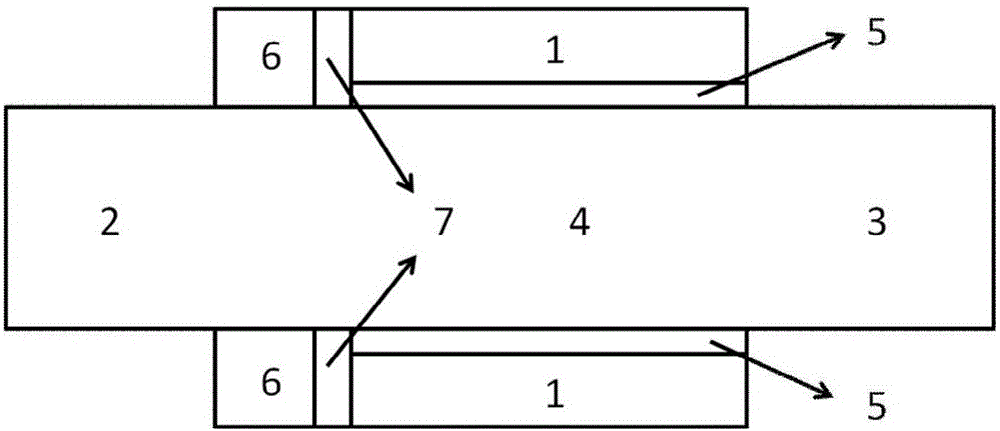

[0016] Such as figure 1 As shown, a new type of P + Sidewall junctionless field effect transistor, including double gate 1, source region 2, drain region 3, channel region 4, gate dielectric layer 5, P + Sidewall 6 and isolation layer 7; wherein, the double gate 1 is located at the upper and lower positions of the channel region 4, and maintains vertical symmetry, the gate dielectric layer 5 is located between the channel region 4 of the double gate 1, and the double gate 1 One side with P + Side wall 6, P + The side wall 6 is a symmetrical structure up and down, and the double gate 1 and the P + An isolation layer 7 is provided between the side walls 6, P + The sidewall 6 is in direct contact with the source region 2 . The doping concentration of source region 2, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com