Platform histogram equalization realization method based on FPGA, and device thereof

A technology of histogram equalization and implementation method, which is applied in image enhancement, image analysis, image data processing, etc., can solve the problems of FPGA power consumption increase and operation speed reduction, so as to save space, increase operation speed, and reduce bit size. wide effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

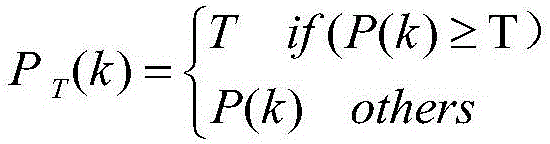

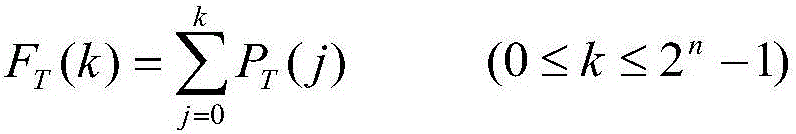

Method used

Image

Examples

Embodiment 1

[0066] The input image with a resolution of 640×512 and a bit width of 12 is used. The FPGA model is EP3C40F484I7, and the upper limit platform value is set to 512. The image is input to the platform histogram equalization module to perform histogram equalization processing on the image.

[0067] Table 1-1 Resource occupancy of the histogram equalization method using two RAMs

[0068]

[0069] Table 1-2 Resource occupation of the present invention

[0070]

[0071] Table 2-1 FPGA resources occupied by the system program using the histogram equalization method of two RAMs

[0072]

[0073]

[0074] Table 2-2 adopts the system program of the present invention to account for the resource situation of FPGA

[0075] Resource Type

[0076] Combining Table 1-1 and Table 1-2, Table 1-1 shows the FPGA resources occupied by the implementation method of using two RAMs to store the statistical histogram and cumulative histogram data generated during the histogram e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com