Multi-source access scheduling method and device for registers of network interface chip

A technology of network interface and scheduling method, applied in the field of register multi-source access scheduling, can solve problems such as difficulty in meeting NIC chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

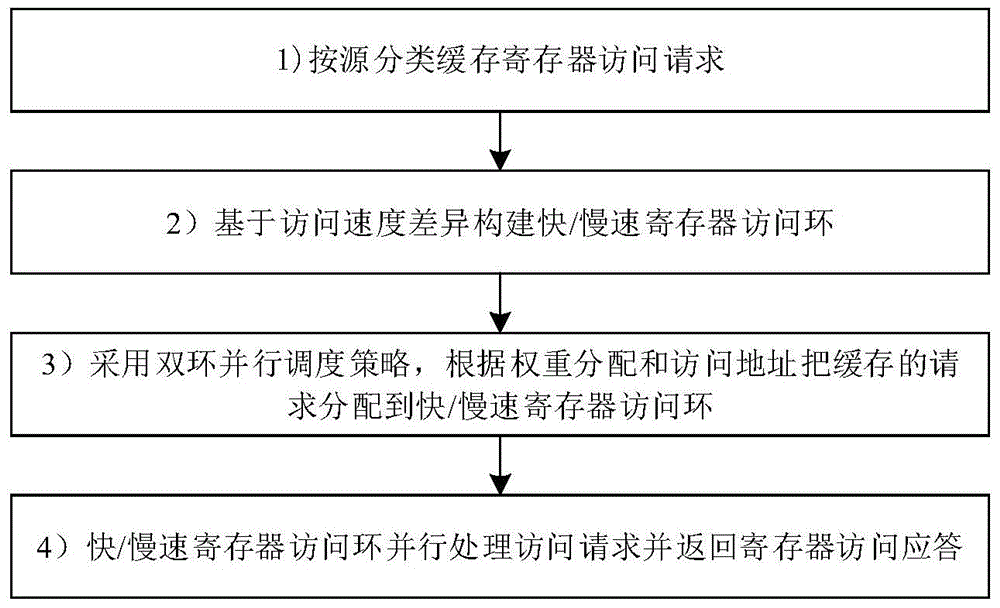

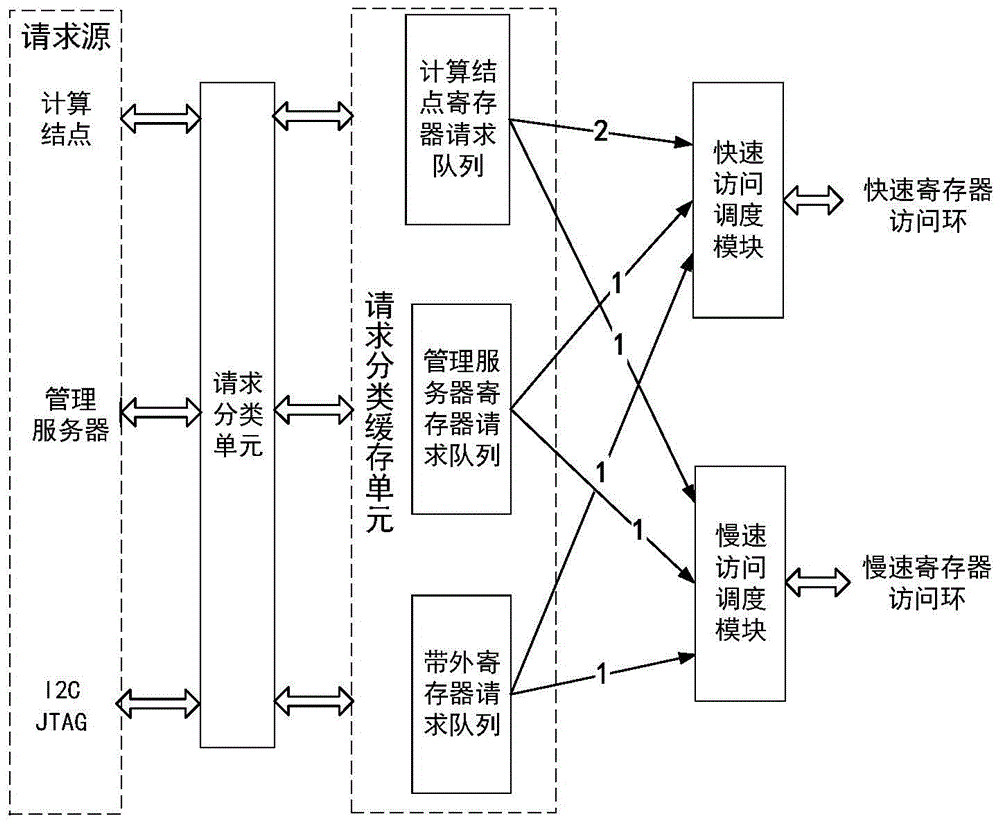

[0044] Such as figure 1 As shown, the implementation steps of the register multi-source access scheduling method for the network interface chip in this embodiment are as follows:

[0045] 1) Cache register access requests by source classification: the request classification unit caches register access requests from multiple request sources to the request classification cache unit according to the type of request source;

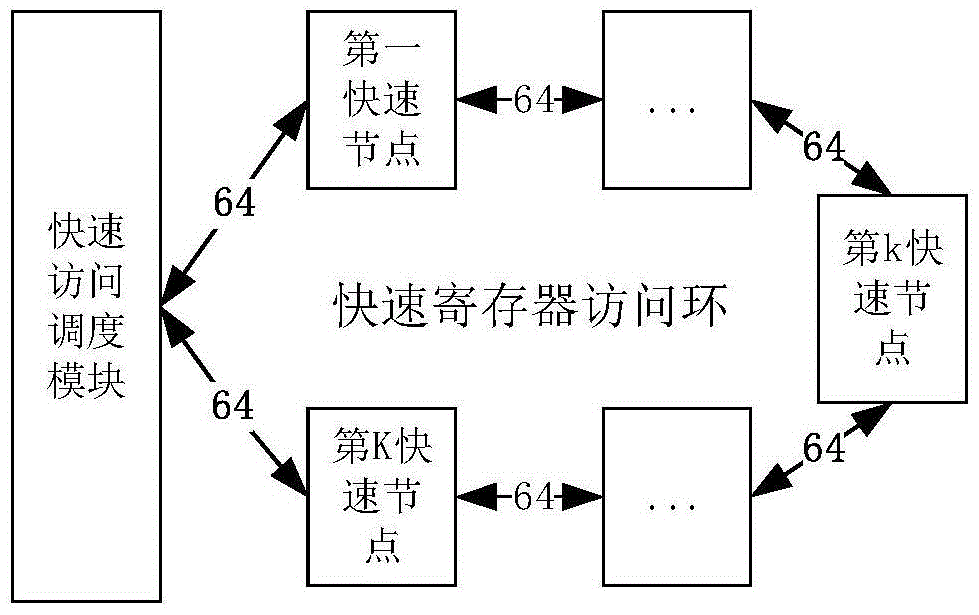

[0046] 2) Build a fast / slow register access ring based on the difference in access speed: the fast access common module pre-connects register modules including user-programmable registers, some control and status registers in series to form a fast register access ring; the slow access common module will not contain The register modules of user-programmable registers, some control and status registers are connected in series to form a slow register access ring;

[0047] 3) A dual-ring parallel scheduling strategy is adopted, and cached requests are assigned t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com