Multi-core processor architecture based on MapReduce programming model

A technology of multi-core processors and programming models, applied in the fields of electrical digital data processing, instruments, computers, etc., which can solve the problems of slow processing speed and achieve the effect of increasing speed, more flexibility, and improving throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037]The present invention will be further described below with reference to the accompanying drawings and in conjunction with specific application programs.

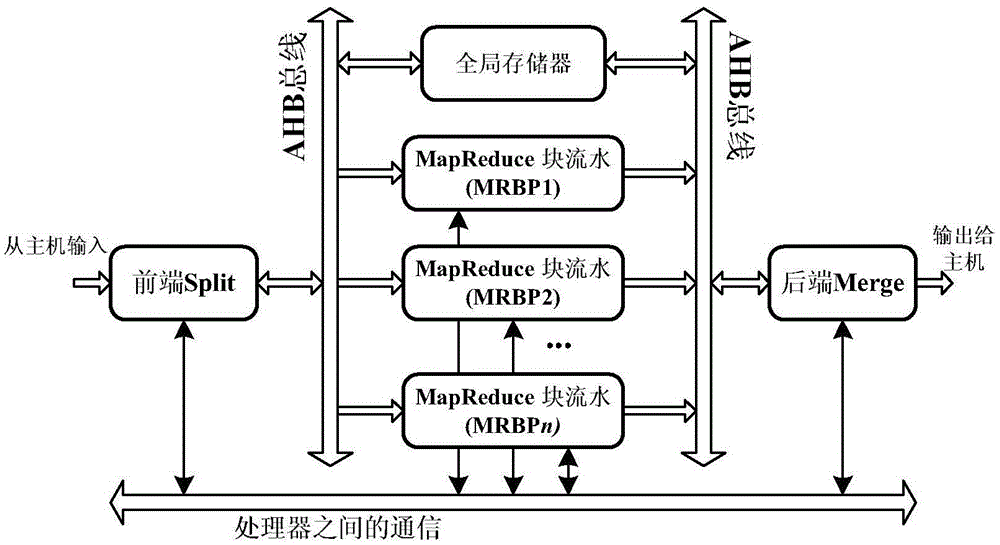

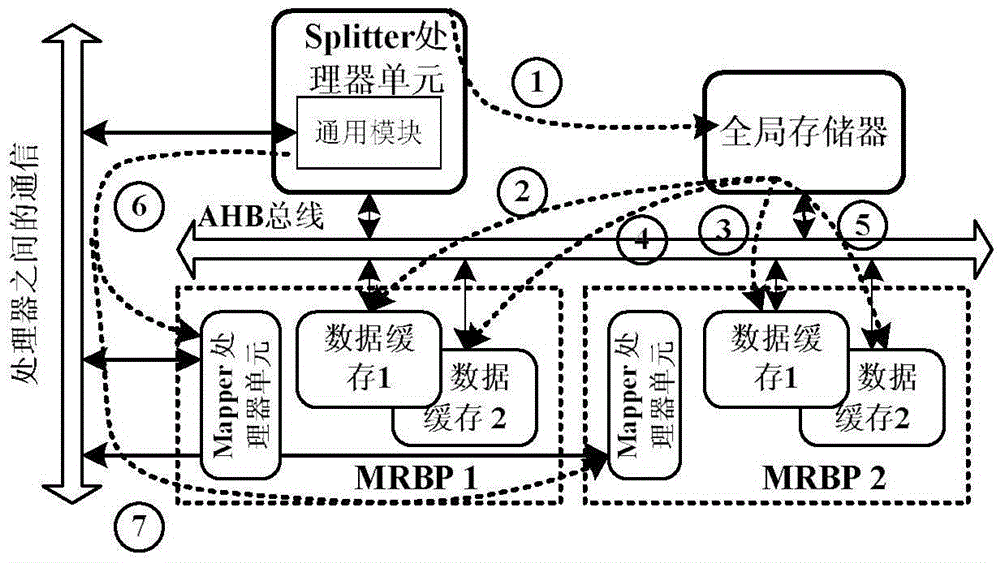

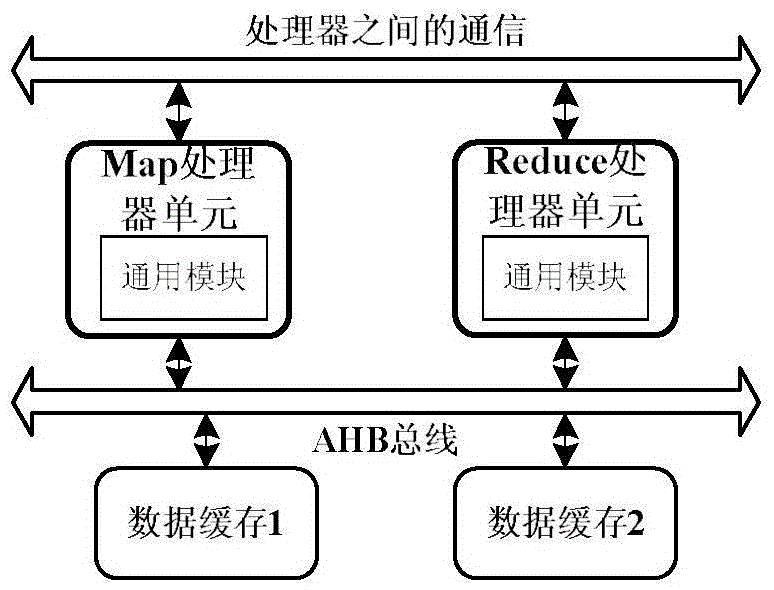

[0038] see figure 1 The invention discloses a multi-core processor architecture based on a MapReduce programming model, which connects processor clusters through a layered interconnection structure. Such as figure 1 As shown, the processor is mainly composed of three parts: the Split module divides the input data and assigns tasks; the MapReduce Block Pipeline (MapReduce Block-Pipe, referred to as MRBP) module composed of multiple block pipelines processes the divided data blocks into the data pair defined by the MapReduce programming model, where key represents the key value, and value represents the number of the key value; the back-end Merge module merges the results of the data pair output by the MRBP module, and All data pairs with the same key value are combined into a data pair.

[0039] Specifically, the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com