Semiconductor device, manufacturing method therefor, and electronic device

A technology for electronic devices and semiconductors, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, and electrical solid-state devices, etc., can solve the problems of increasing the number of steps, increasing product costs, affecting shipments, etc., to increase shipments, The effect of reducing process cost and reducing the risk of leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

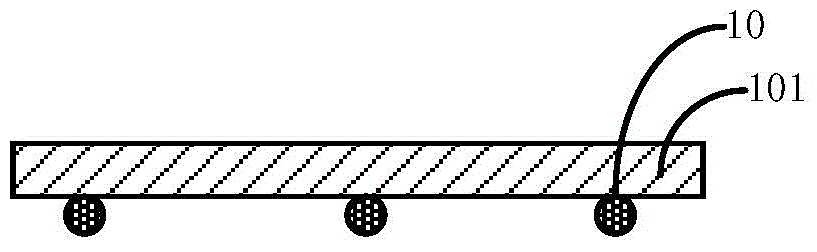

[0048] Current methods of fabricating semiconductor devices such as Figures 1a-1d As shown, wherein, a first wafer 101 is provided first, and a bump generation process (Bump) is performed to form several bonding bumps 10 on the first wafer 101, as Figure 1a shown.

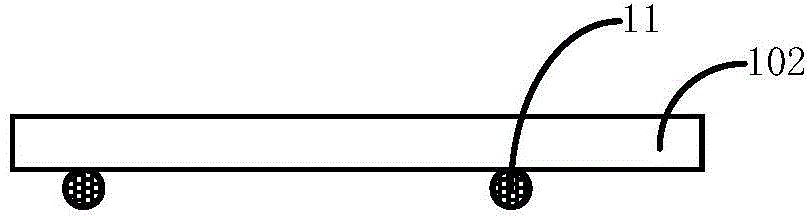

[0049] Then a second wafer 102 is provided, and a bump generation process (Bump) is also performed to form several bonding bumps 11 on the second wafer 102, such as Figure 1bshown.

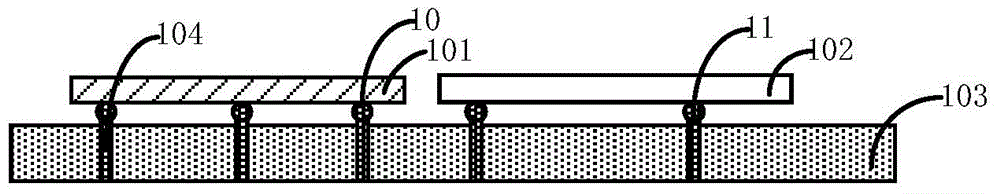

[0050] A third wafer 103 is provided, wherein a number of through-silicon vias 104 (TSVs) are formed in the third wafer 103 for realizing connections, such as Figure 1c shown.

[0051] Alternatively, the third wafer 103 is selected as an interposer, and the first wafer 101, the second wafer 102, and the third wafer 103 are connected together through a flip-chip bump process (Bump) for signal transmission. Such as Figure 1d shown. However, the method not only increases the number of steps in the process and increases the cost ...

Embodiment 1

[0054] In order to solve the problems in the prior art, the present invention provides a method for preparing a semiconductor device, the following in conjunction with the attached Figure 2a-2f The method is described further.

[0055] First, step 201 is performed to provide a bottom wafer 201 .

[0056] Specifically, such as Figure 2a As shown, the bottom wafer 201 may be a memory wafer, for example, various memory devices or units may be formed on the bottom wafer.

[0057] Optionally, other active or passive devices may also be formed in the bottom wafer, and are not limited to a certain one, which will not be repeated here.

[0058] Step 202 is executed to form an insulating layer 202 on the bottom wafer 201 .

[0059] Specifically, such as Figure 2b As shown, in this step, an insulating layer 202 is formed on the bottom wafer 201 to completely cover the bottom wafer 201. Optionally, the insulating layer 202 is made of an organic insulating material, which can not o...

Embodiment 2

[0091] The present invention also provides a semiconductor device, comprising:

[0092] bottom wafer 201;

[0093] an insulating layer 202 located above the bottom wafer;

[0094] interconnection vias 20 located in the insulating layer and connected to the bottom wafer;

[0095] The top wafer 203 is located above the insulating layer, wherein bumps 204 are formed on the top wafer, and the bumps are connected to the interconnection vias.

[0096] Wherein, the bottom wafer 201 may be a storage wafer, for example, various storage devices or units may be formed on the bottom wafer. Optionally, various active or passive devices may also be formed on the bottom wafer, and are not limited to a certain one, which will not be repeated here.

[0097] The insulating layer 202 is made of an organic insulating material, which not only reduces the risk of electric leakage, but also improves the breakdown resistance. Optionally, the insulating layer 202 may be polyimide.

[0098] In the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com