Fabrication method of circuit board solder mask layer

A manufacturing method and circuit board technology, which are applied in the directions of printed circuit manufacturing, printed circuit, and non-metallic protective layer coating, etc., can solve the problems of speeding up circuit boards, dropping bridges, breaking bridges, etc., so as to improve the firmness and not easily drop bridges , the effect of increasing the binding force

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

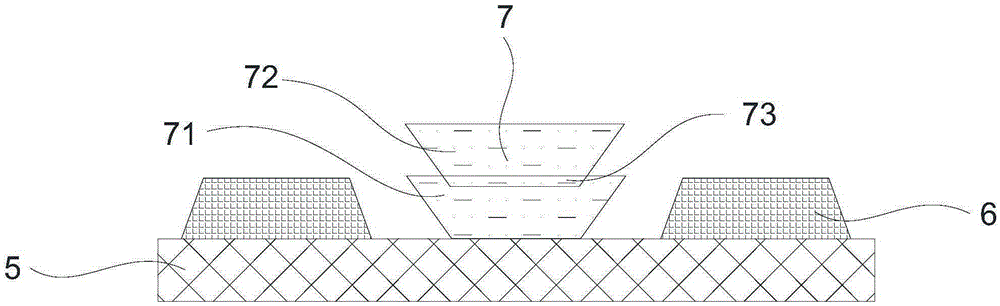

[0030] Solder Mask Requirements

[0031] Solder resist ink thickness: 10-30μm;

[0032] Solder resist bridge width: 50μm≤solder resist bridge width≤75μm.

[0033] The manufacturing process of the circuit board solder mask layer is as follows:

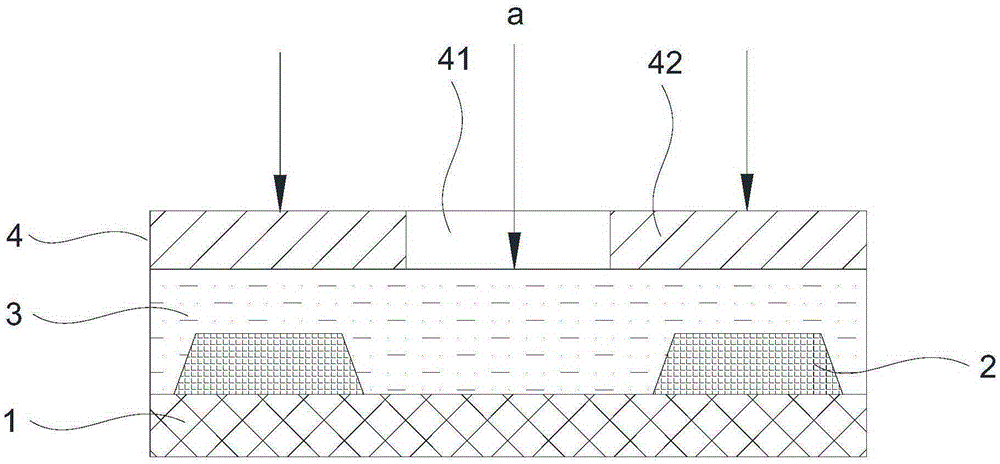

[0034] Cover the solder resist ink with silk screen printing on the surface of the circuit board, and then pre-bake the solder resist ink at 75±5°C for 45 minutes to cure the solder resist ink to ensure that the thickness of the solder resist ink is 8-15 μm after curing.

[0035] Cover the surface of the cured solder resist ink with a film sheet for the first exposure, and the exposure step uses 300-320mj / cm 2 Exposure energy exposure 7s.

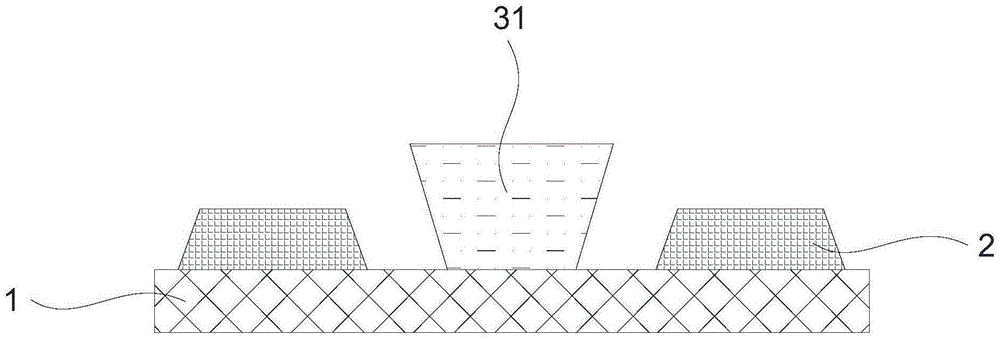

[0036] After the first exposure, the circuit board passes through the spray development line with a length of 6m, and the solder resist ink in the unexposed area is washed away by the developing solution; the speed of the circuit board passing through the spray development line is 3.5m / min, and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com