Formation method of nand flash memory device

A technology of flash memory devices and core devices, which is applied in the field of formation of NAND flash memory devices, can solve problems such as poor performance of NAND flash memory devices, and achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] As stated in the background technology, the performance of NAND flash memory devices formed by existing methods is not good, and the reasons are as follows:

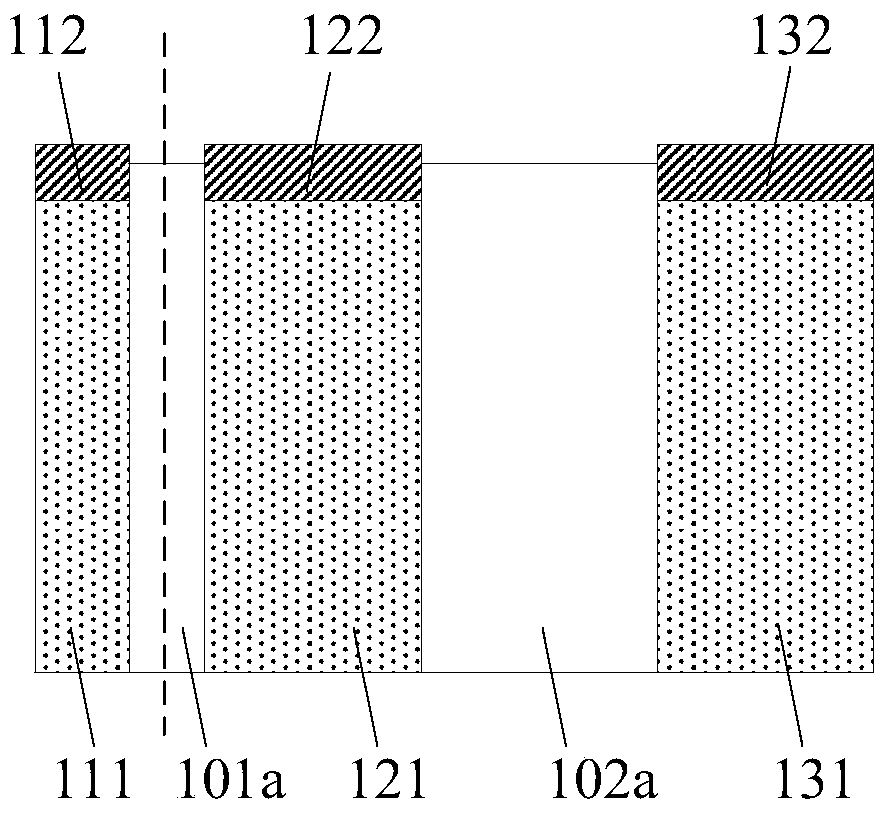

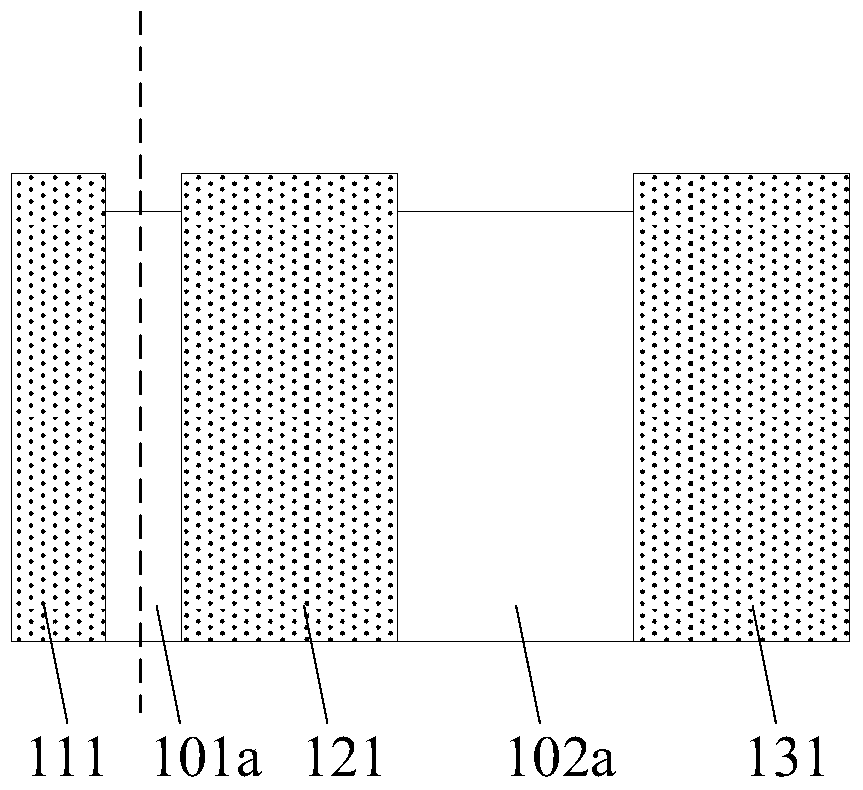

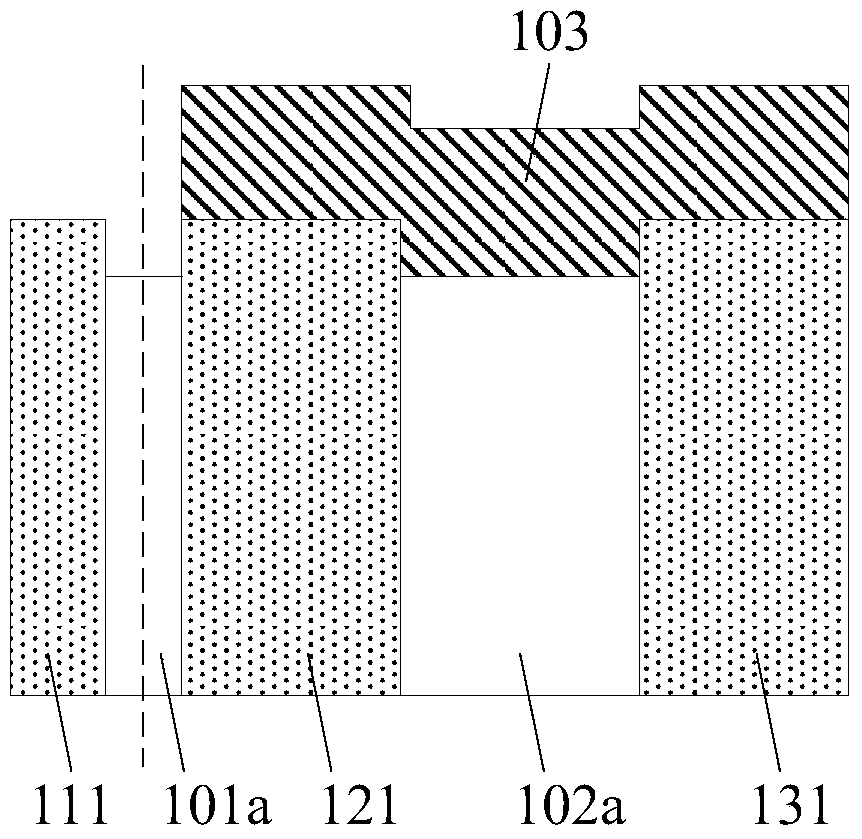

[0037] when to Figure 1 to Figure 4 After the NAND flash memory device is formed by the method shown, it is found through the transmission electron microscope that the sidewall of the first gate 111 in the NAND flash memory device is not flat, and further analysis shows that after the trench 104 is formed, the gate 111 is obviously damaged; it turns out In the process of forming the trench 104, the corresponding etching process will cause a certain etching effect on the sidewall of the first gate 111, resulting in that the subsequent ONO layer cannot be well covered on the sidewall of the first gate 111, and This further causes performance degradation of the NAND flash memory device.

[0038]In addition, in the existing method, the photoresist layer 103 is formed after removing the second hard mask layer 122 and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com