Fan-out type packaging structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of low yield rate and high packaging cost, so as to improve yield rate, save materials, avoid thinning and The effect of the laser drilling process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

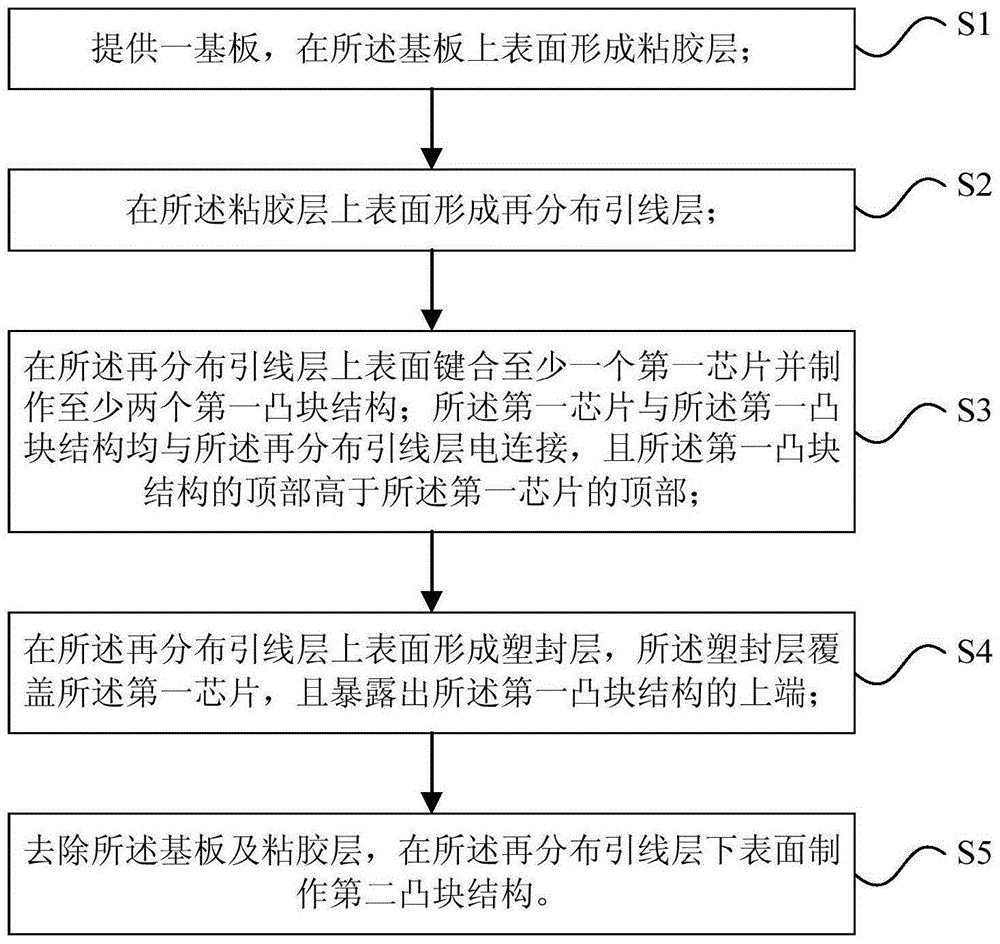

[0078] The present invention provides a method for manufacturing a fan-out packaging structure, please refer to figure 1 , shown as a process flow diagram of the method, comprising the following steps:

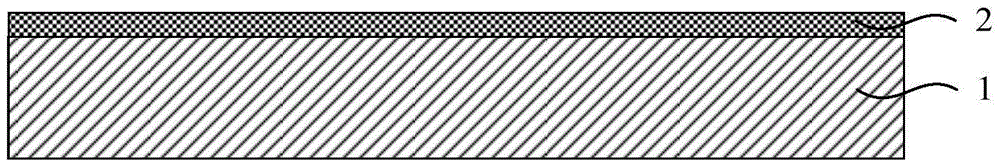

[0079] S1: providing a substrate, forming an adhesive layer on the upper surface of the substrate;

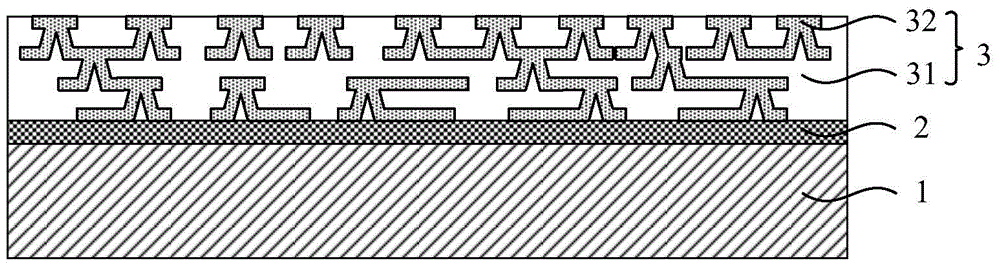

[0080] S2: forming a redistribution lead layer on the upper surface of the adhesive layer;

[0081] S3: bonding at least one first chip on the upper surface of the redistribution wiring layer and fabricating at least two first bump structures; both the first chip and the first bump structure are connected to the redistribution wiring layer electrically connected, and the top of the first bump structure is higher than the top of the first chip;

[0082] S4: forming a plastic sealing layer on the upper surface of the redistribution lead layer, the plastic sealing layer covers the first chip and exposes the upper end of the first bump structure;

[0083] S5: removing the substr...

Embodiment 2

[0115] The present invention also provides a fan-out packaging structure, such as Figure 12 As shown, it is a schematic diagram of the fan-out package structure, including:

[0116] Redistribute lead layer 3;

[0117] At least one first chip 4 bonded to the upper surface of the redistribution wiring layer 3 and electrically connected to the redistribution wiring layer 3;

[0118] At least two first bump structures 5 that are electrically connected to the redistribution lead layer 3 and whose tops are higher than the first chip 4;

[0119] Covering the first chip 4 and exposing the plastic sealing layer 6 on the upper end of the first bump structure 5;

[0120] And the second bump structure 7 fabricated on the lower surface of the redistribution lead layer 3 .

[0121] Specifically, the redistribution lead layer 3 includes a dielectric layer 31 and at least one layer of redistribution metal lines 32 formed in the dielectric layer 31 . As an example, the redistribution lead...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com