Gate driving circuit and driving method thereof as well as display device

A gate drive circuit and drive method technology, applied in static indicators, instruments, etc., can solve the problems of received signal strength attenuation, signal delay, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

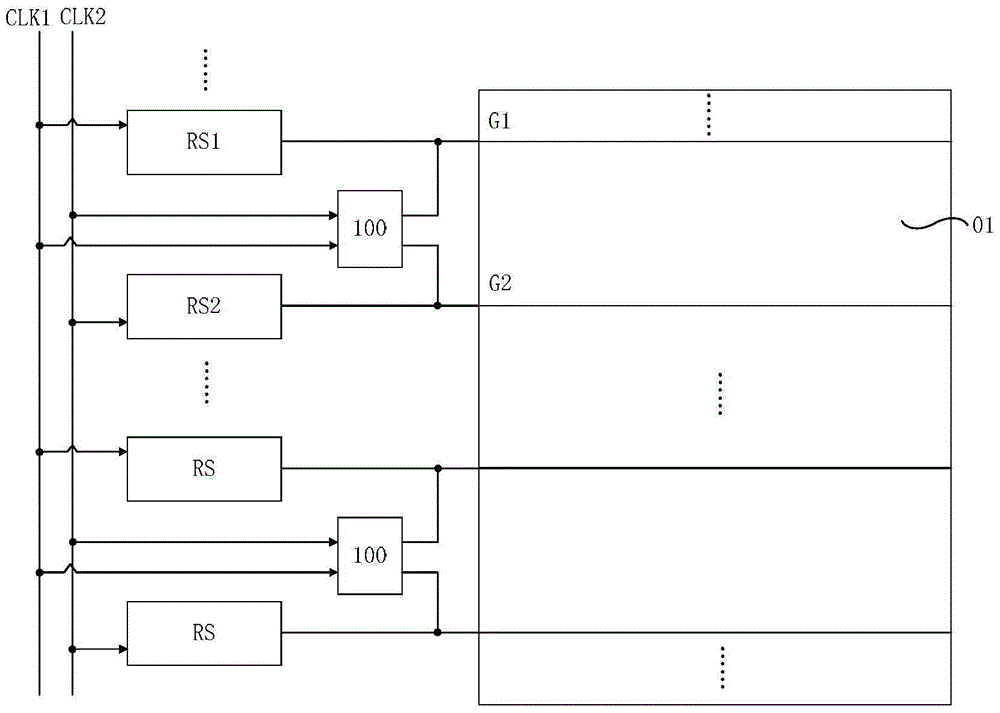

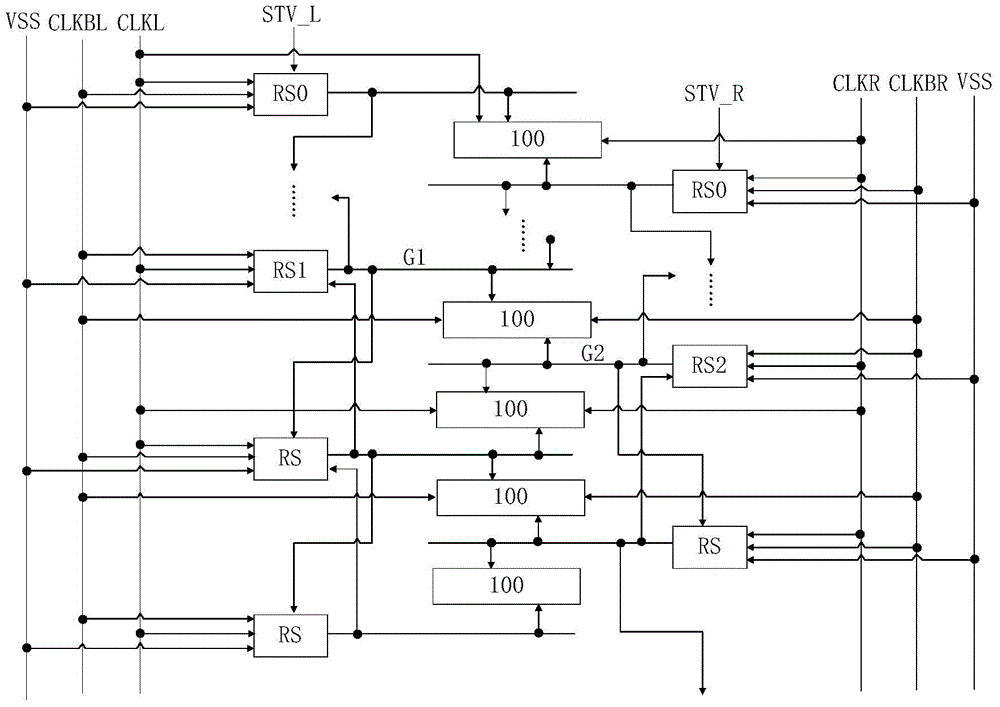

[0061] The structure of the pre-charging unit 100 in this embodiment is as follows Image 6 As shown, it includes a first transistor T1, a second transistor T2 and a third transistor T3.

[0062] Wherein, the gate and the first pole of the first transistor T1 are connected to the second clock signal terminal CLK2, and the second pole is connected to the gate of the second transistor T2.

[0063] The first pole of the second transistor T2 is connected to the first gate line G1, and the second pole is connected to the gate of the third transistor T3.

[0064] A first pole of the third transistor T3 is connected to the first clock signal terminal CLK1, and a second pole is connected to the second gate line G3.

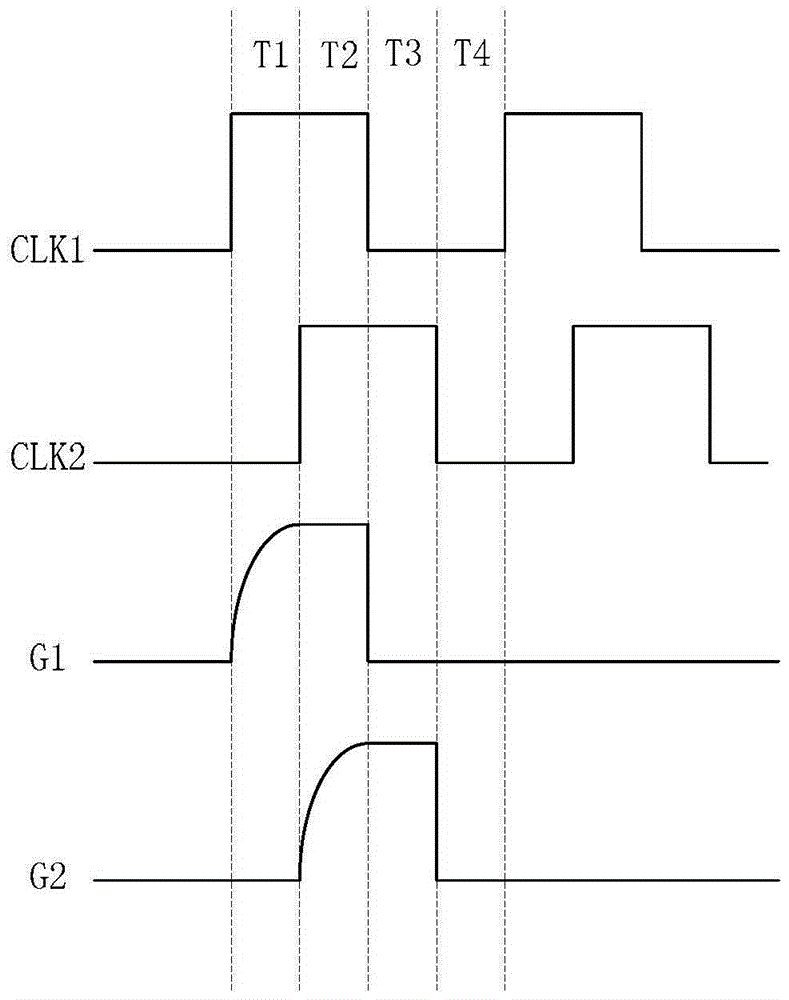

[0065] In this way, if figure 2 As shown, at the second moment T2, the second clock signal terminal CLK2 outputs a high level, which turns on the first transistor T1, so that the second clock signal terminal CLK2 outputs a high level through the first transistor T1 to ...

Embodiment 2

[0067] The structure of the pre-charging unit 100 in this embodiment is as follows Figure 7 As shown, it can be seen that the pre-charging unit 100 in this embodiment includes all the transistors in the first embodiment (namely, the first transistor T1, the second transistor T2 and the third transistor T3), and in addition, the pre-charging unit 100 also includes The fourth transistor, and the pre-charging unit 100 is connected to the start signal terminal STV.

[0068] Wherein, the gate of the fourth transistor is connected to the start signal terminal STV, the first pole is connected to the gate of the second transistor T2, and the second pole is connected to the reset voltage terminal VSS. Wherein, the reset voltage terminal VSS can generally be input with a low level or be grounded. In this way, when the pre-charging unit 100 performs the pre-charging action, the fourth transistor T4 can be used to Figure 7 Reset the potential at the node PU in order to prevent the res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com