Junction field effect transistor and method of making same

A technology of field effect transistors and junctions, applied in the preparation of junction field effect transistors, in the field of junction field effect transistors, can solve the problem of high pinch-off voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

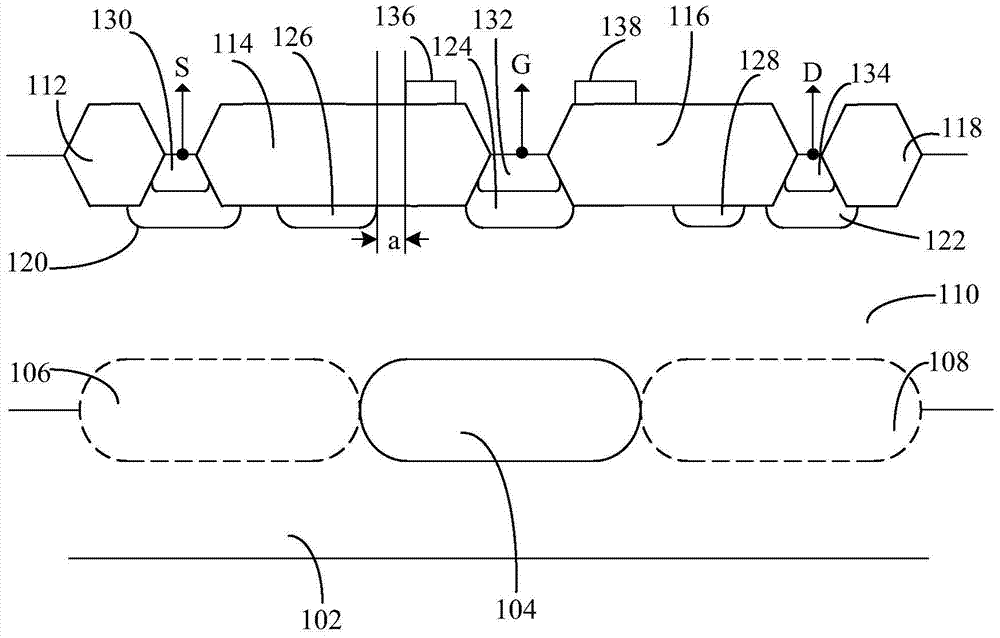

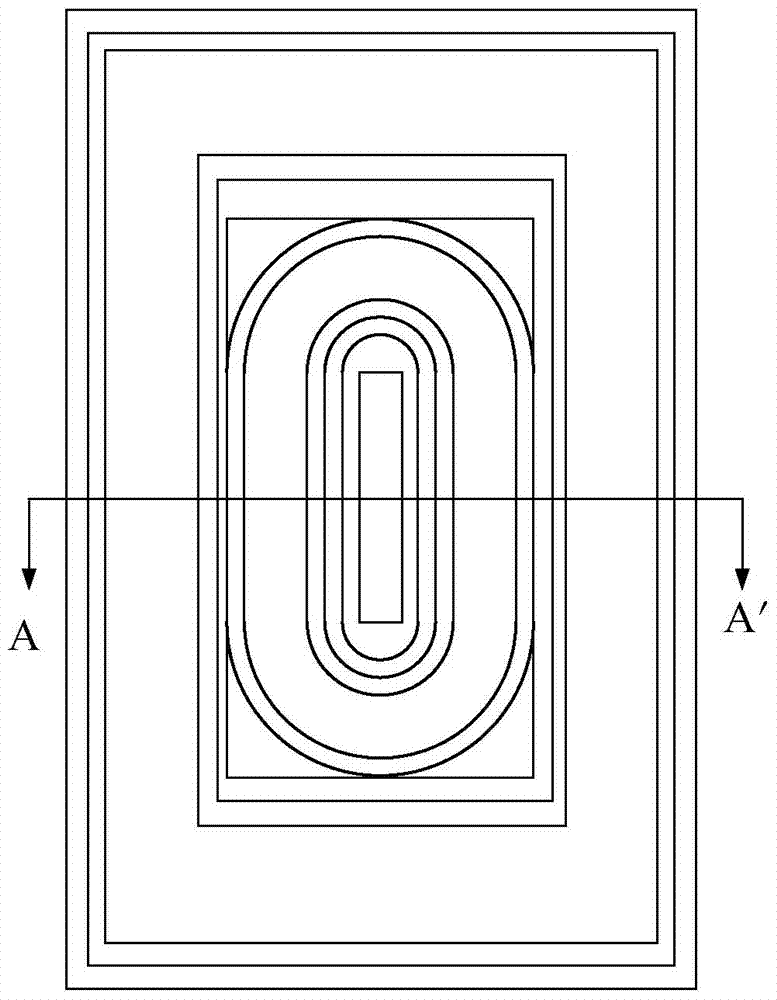

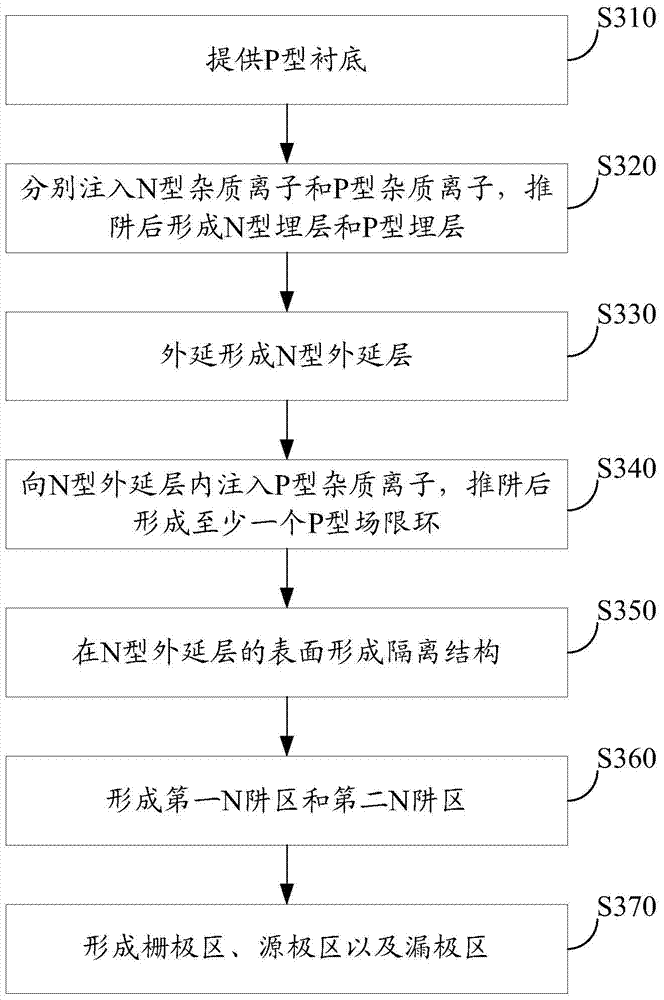

[0019] In order to make the objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings. In this specification and drawings, reference signs N and P assigned to layers or regions indicate that these layers or regions include a large number of electrons or holes, respectively. Further, the reference marks + and − assigned to N or P indicate that the concentration of the dopant is higher or lower than in layers not so assigned to the marks. In the following description of the preferred embodiments and the drawings, similar components are assigned similar reference numerals and redundant descriptions thereof are omitted here.

[0020] A junction field effect transistor, comprising: a P-type substrate; a P-type buried layer and an N-type buried layer placed on the P-type substrate. Wherein, the N-type buried layer is respectively pla...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com