Design method for increasing PCB yield

A design method and yield rate technology, applied in the electronic field, to achieve the effect of controlling R&D costs and improving yield rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

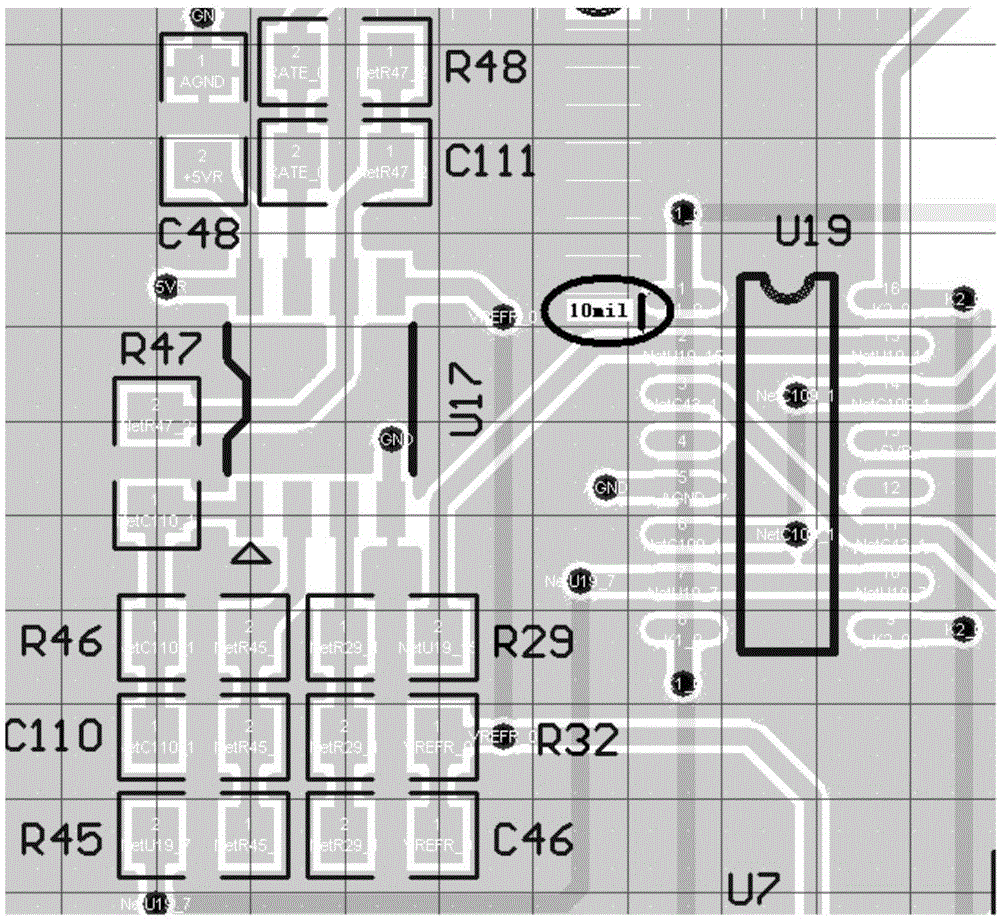

[0017] An embodiment proposed by the present invention effectively improves the yield of PCB by changing the distance between device pins and copper cladding on the printed circuit board, thereby effectively controlling the research and development cost of the entire project.

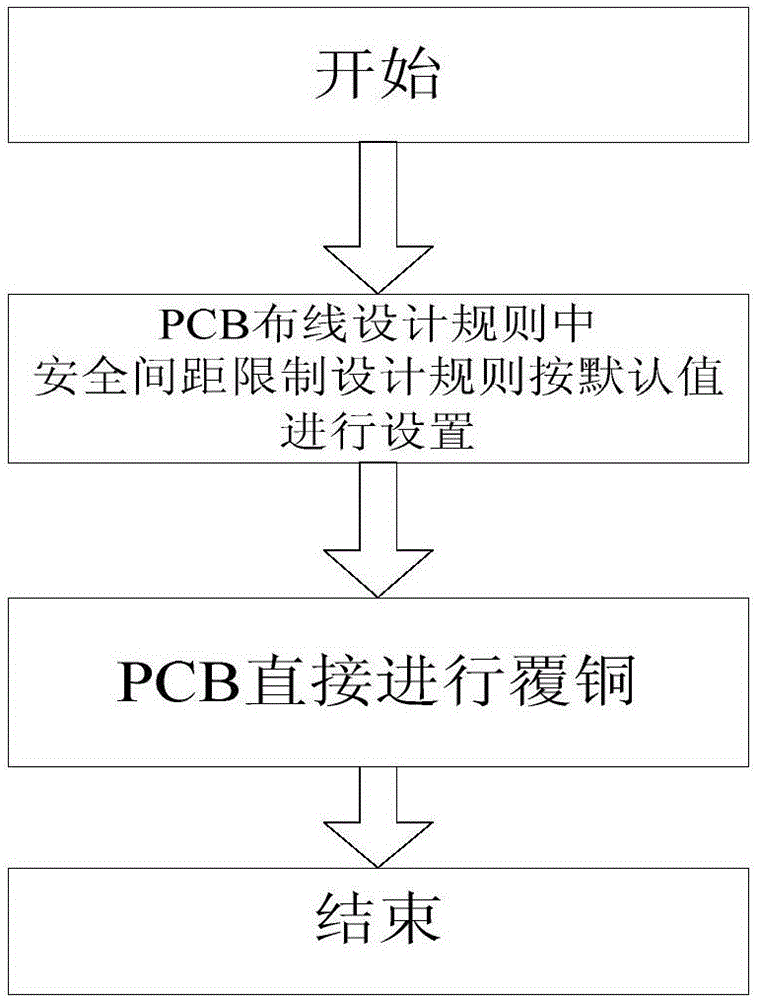

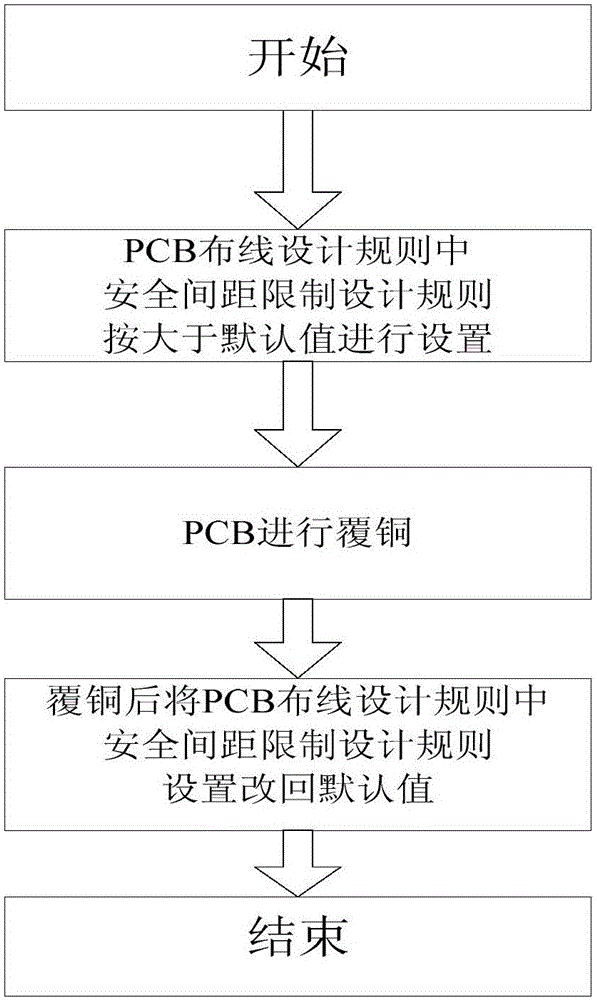

[0018] The concrete design process of PCB of the present invention is as figure 2 , the design steps are as follows:

[0019] 1) Carry out PCB wiring according to the PCB wiring process;

[0020] 2) Set the safety spacing adjustment in the PCB layout design rules to be greater than the default value;

[0021] 3) The PCB is covered with copper, so that when the copper is poured, the new rules between the pin and the li...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com