Distributed algorithm applied to FIR filters

A distributed algorithm and filter technology, applied in impedance networks, digital technology networks, electrical components, etc., can solve the problems of multipliers occupying large resources, reducing memory, and low FPGA resource utilization, saving logic units and memory. resources, the effect of fully efficient FPGA resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The specific implementation manner and working principle of the present invention will be described below in conjunction with the accompanying drawings.

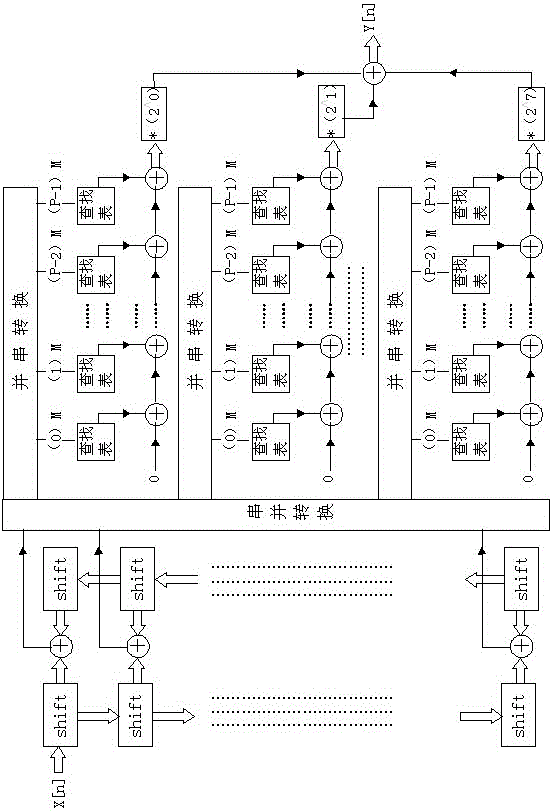

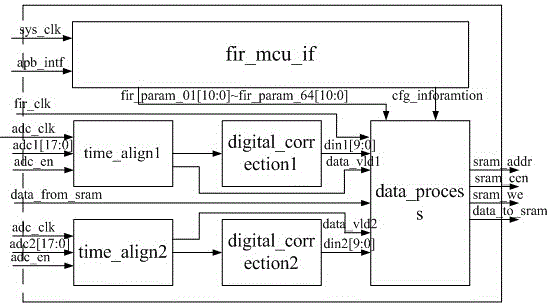

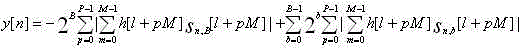

[0015] Such as figure 2 As shown, it is a flow chart of the steps of applying the distributed algorithm of the present invention to the existing FIR filter. The binary bit weight multiplication module is also used in the realization of the method. The distributed algorithm includes the following steps: (1) analog input The signal X[n] is input to the FIR filter, and the analog input signal X[n] is converted by an analog-to-digital conversion module to obtain a B-bit digital signal, where B is a positive integer; (2) The B-bit digital signal is used as an input Data goes into the shift register. The shift register sends the processing result to the serial-parallel module; (3) the serial-parallel module transmits the input data to the binary weight multiplication module, which rearranges the output to the parallel-ser...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com