Error correction protection architecture and method applied to resistive random access memory cache of solid state disk

A technology of resistive variable memory and solid-state hard disk, which is applied in the direction of static memory, digital memory information, information storage, etc. It can solve the problems of fast read and write speed, high static power consumption, large leakage current, etc., and achieve system performance improvement and hit rate improvement rate, speed-up effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention is described in further detail below in conjunction with accompanying drawing:

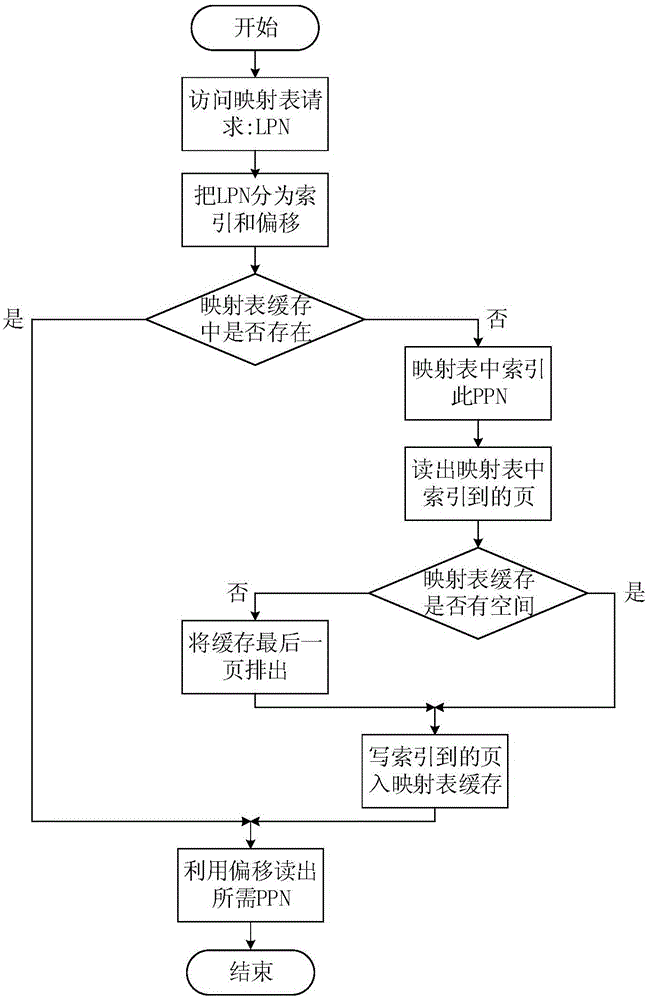

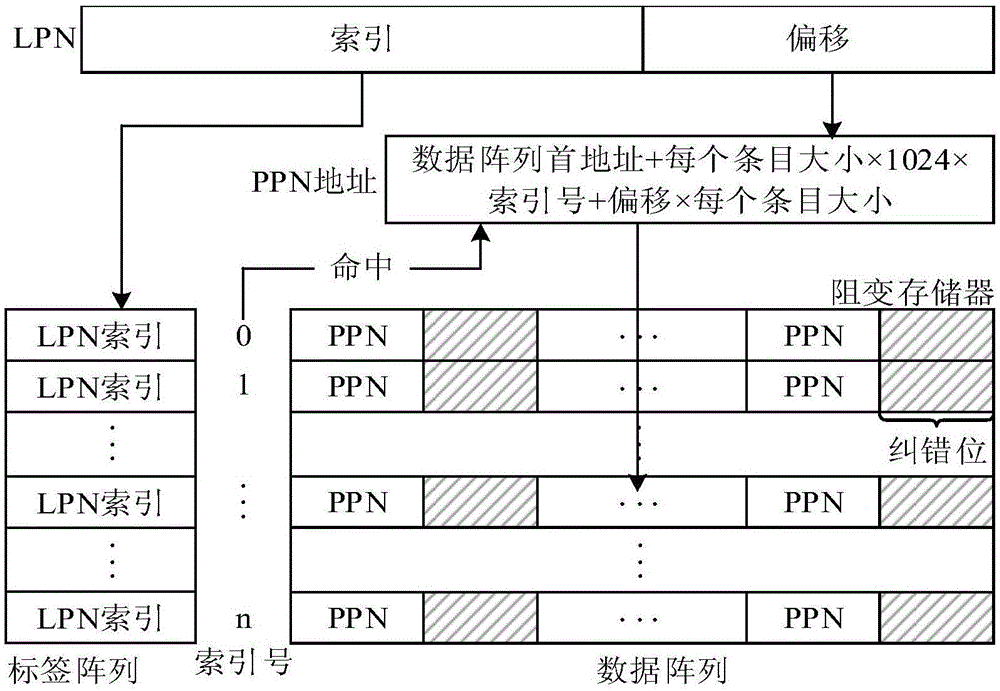

[0022] refer to figure 1 , the code length of the coarse-grained management mapping table in the error correction protection architecture applied to the solid-state hard drive resistive memory cache described in the present invention is the same as the code length of the page cache data, and in the data processing process, the coarse-grained management mapping The address information of the mapping table whose access frequency is greater than the preset value in the table is stored in the mapping table cache of fine-grained management. The entry of a mapping table of coarse-grained management is composed of 1024 address mapping tables. The mapping table cache of fine-grained management Each entry in contains a mapping table information and an error correction code redundancy of the mapping table information; the exchange data between the fine-grained management mapping...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com