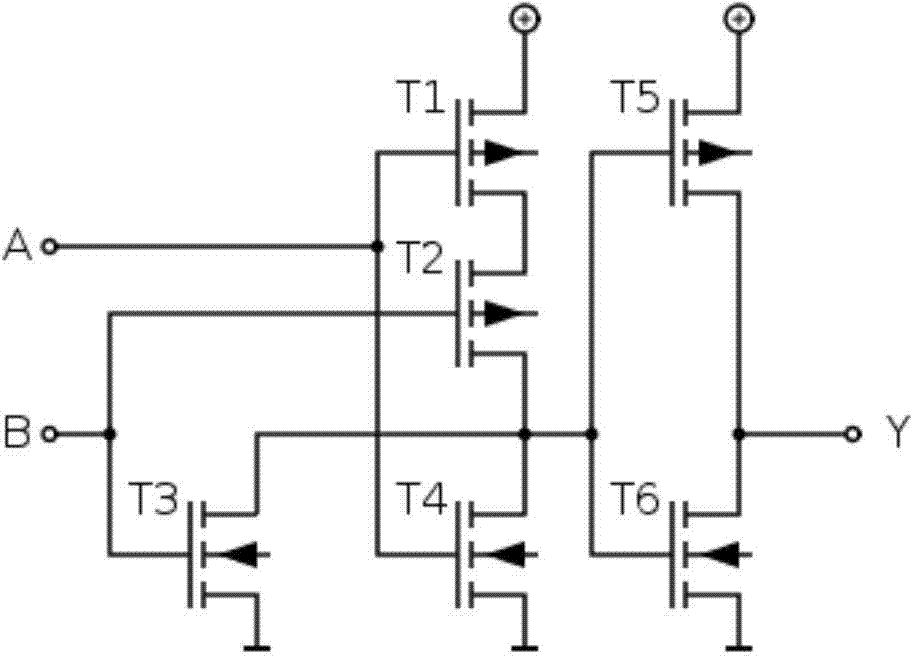

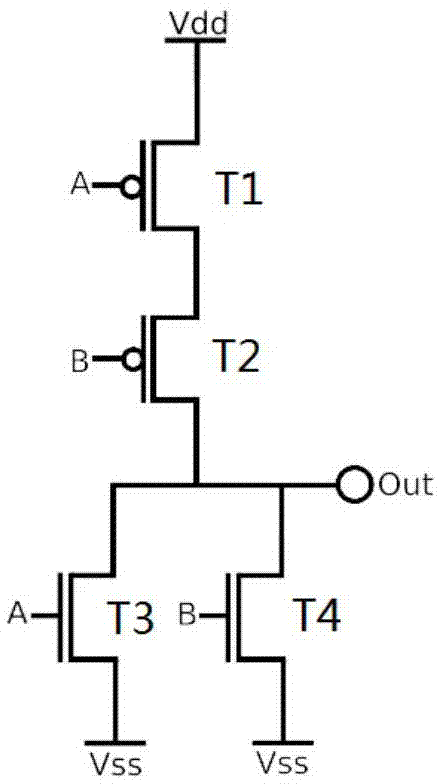

Structures and manufacturing methods of or logic and nand logic devices

A logic device, non-logic technology, applied in the field of integrated circuit manufacturing, can solve the problems of high cost, complex circuit structure, large chip area, etc., achieve simple timing control, simple device and circuit structure, and reduce circuit signal delay. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

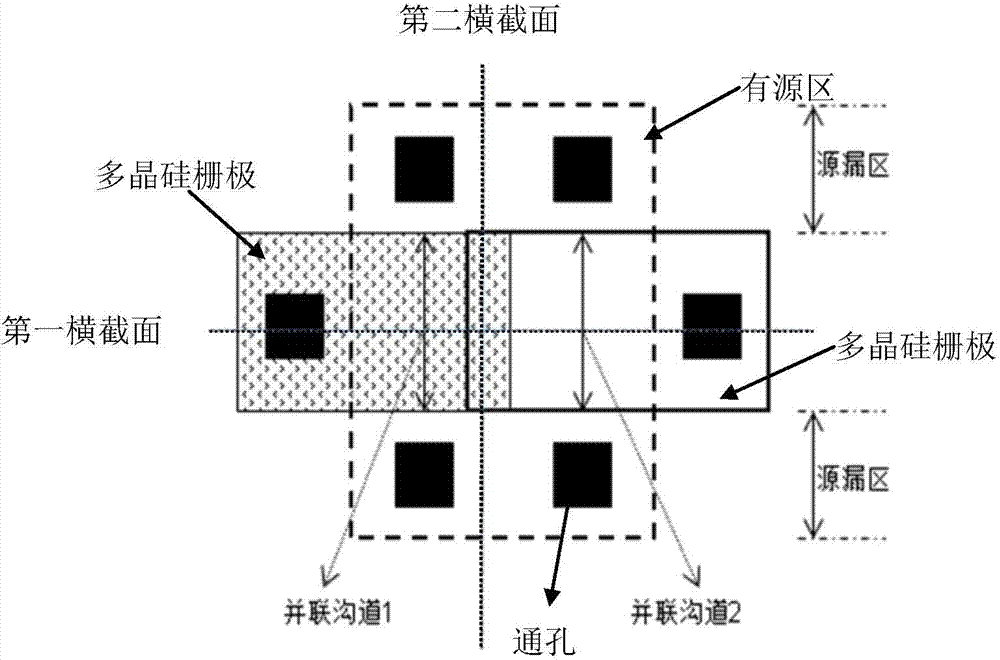

[0038] In order to have a more specific understanding of the technical content, characteristics and effects of the present invention, now in conjunction with the accompanying drawings, the details are as follows:

[0039] OR logic device structure of the present invention, see image 3 , 4 shown.

[0040] Or logic devices, fabricated in a p-well or p-type substrate, with two parallel and adjacent gate gates on it, each controlling the adjacent n-type conduction channel below it. In the direction along the boundary line between the two gate control gates, there is an n-type source region and a drain region at both ends of the gate control gate. In this way, two parallel n-type channels are formed by using the source and drain as leads. There is a polysilicon gate on each of the two gates. The two polysilicon gates can be spaced apart, adjacent to each other or overlap each other, but they must be electrically isolated from each other and independently drawn out as two input ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com