Wafer level chip packaging method

A wafer-level chip and packaging method technology, which is applied in the manufacturing of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., can solve problems such as easy falling off of low-temperature oxide layers

- Summary

- Abstract

- Description

- Claims

- Application Information

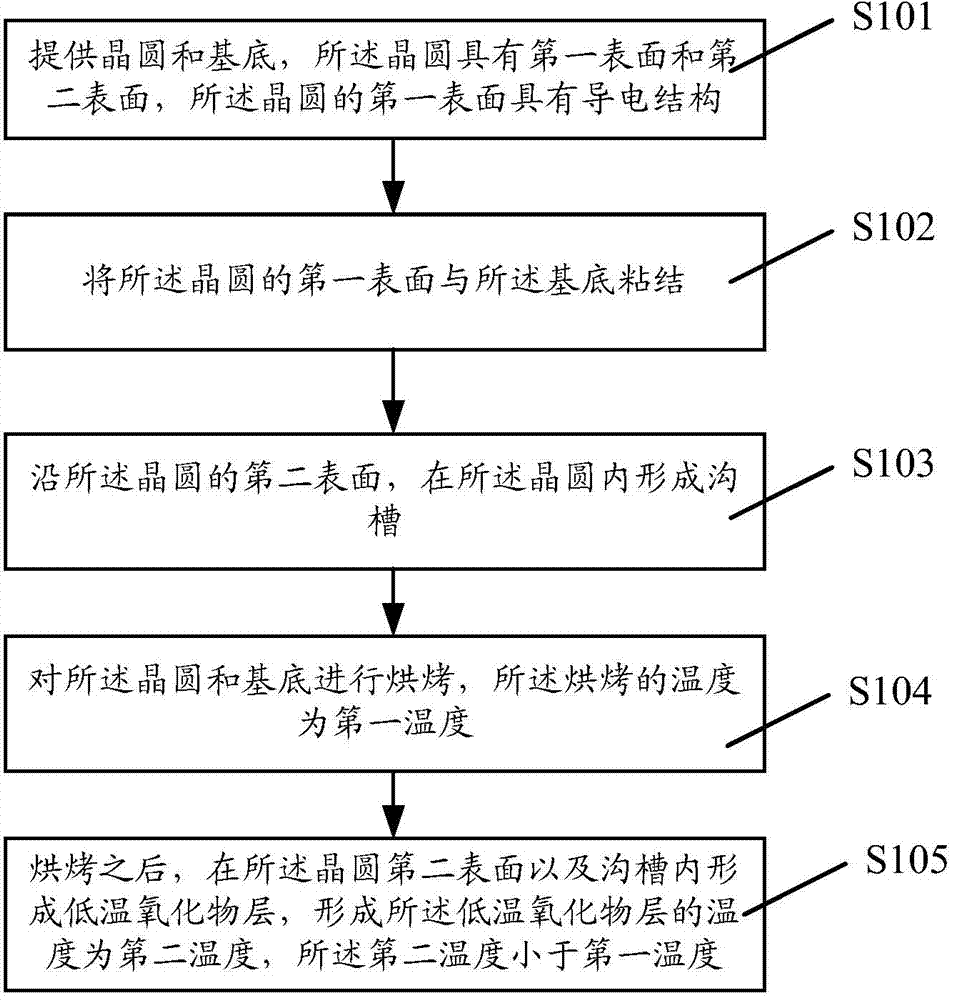

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

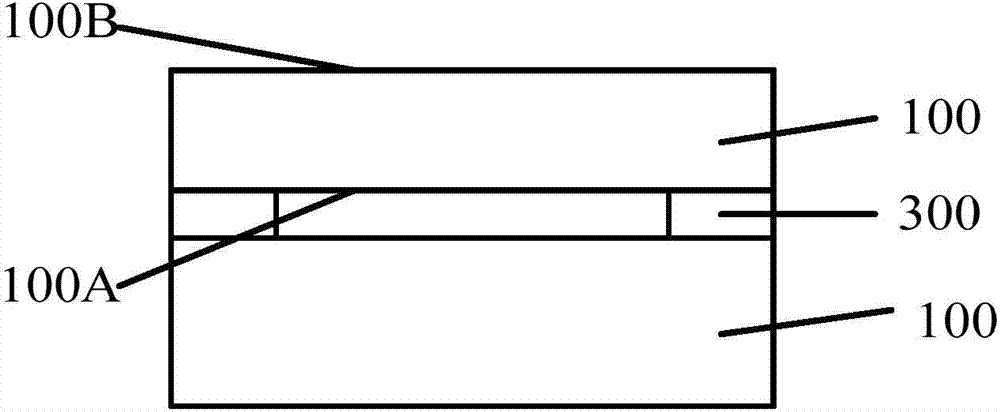

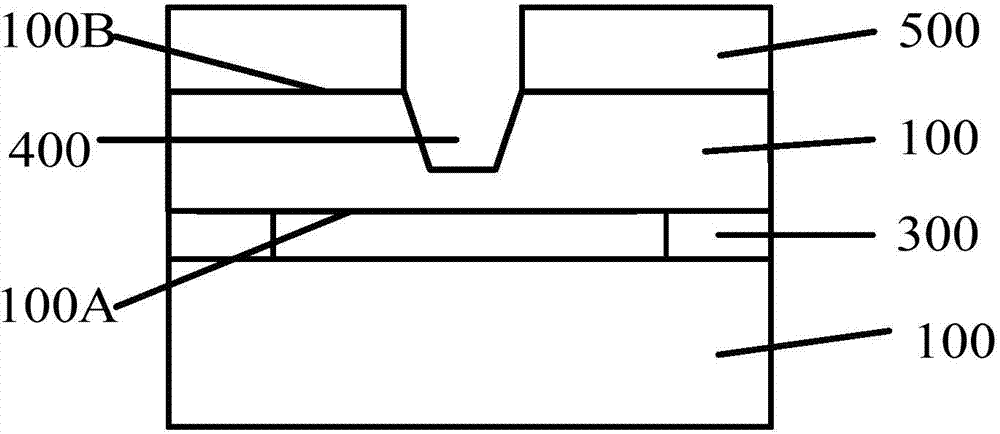

Embodiment Construction

[0033] In the existing wafer-level packaging method, it is necessary to form a layer of low-temperature oxide layer on the surface of the semiconductor wafer as an isolation layer, so as to isolate the wafer from the conductive structure subsequently formed on the surface of the semiconductor wafer. However, it is found in the actual manufacturing process that the bonding strength between the isolation layer formed on the surface of the semiconductor wafer and the semiconductor wafer by using the existing technology is poor, and the phenomenon that the isolation layer peels off from the semiconductor wafer often occurs, which seriously reduces the Stability of semiconductor devices formed after packaging.

[0034] After research, it is found that in the existing wafer-level chip packaging method, the reason why the low-temperature oxide layer on the surface of the wafer is easy to peel off is:

[0035] In the existing wafer-level chip packaging method, the adhesive used to bon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com