Memory chip scrambling verification method

A technology of a memory chip and a verification method, applied in the field of integrated circuit failure analysis, can solve problems such as the inoperability of the memory area, and achieve the effect of accurate scrambling verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The memory chip scrambling code verification method of the present invention, its realization steps are as follows:

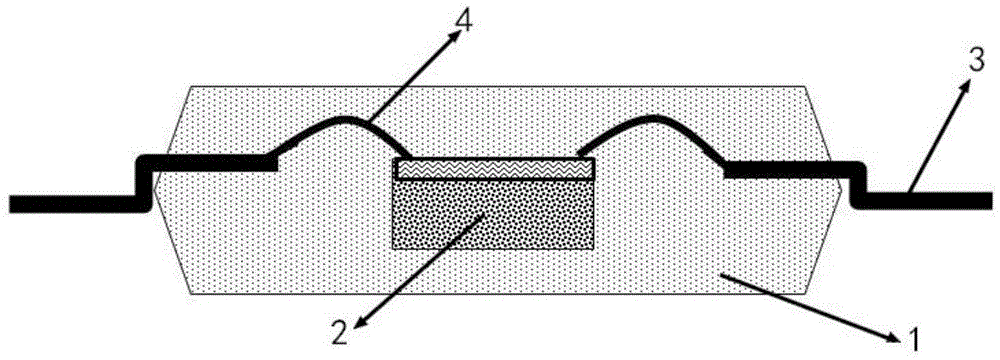

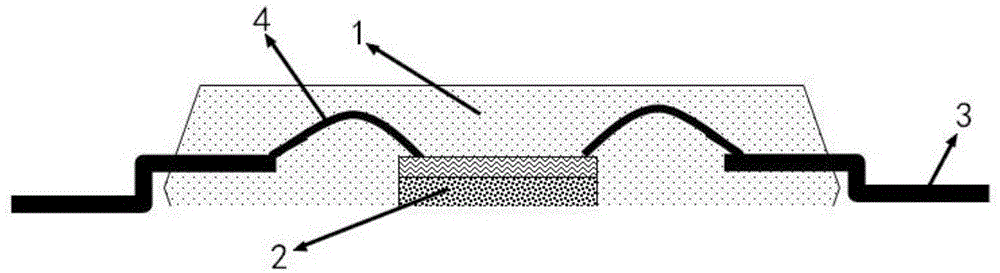

[0026] The first step is to select a sample chip and grind the sample chip from the back side. If it is a bare chip, first package the chip; if it is a packaged chip, it can be used directly, see figure 1 As shown in the figure, 1 is the package body, 2 is the chip, 3 is the pin, and 4 is the connecting wire. Grinding is carried out from the back of the package body 1, and according to the thickness of the chip, 5-200 μm is roughly ground first, leaving about 2-20 μm. like figure 2 .

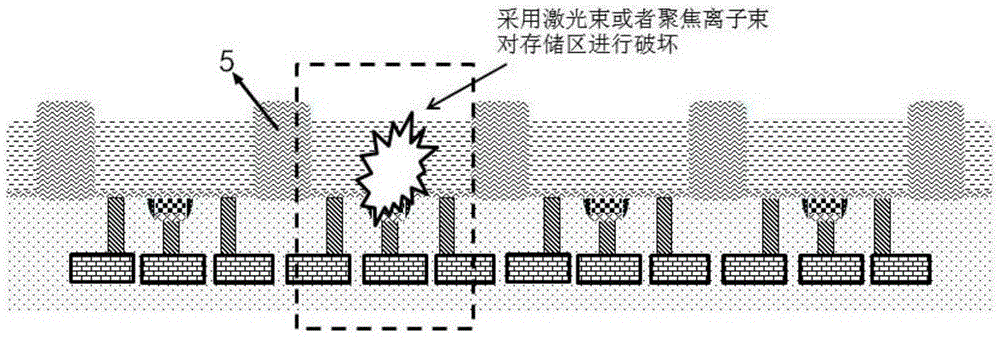

[0027] In the second step, the chemical etching method is used to continue etching the back surface until the insulating isolation layer 5 is exposed, such as image 3 . Some isolation layers are LOCOS (Local Oxide Layer) and some are STI (Shallow Trench Isolation). The purpose of exposing the insulating layer is to determine the location of the memory and the optio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com