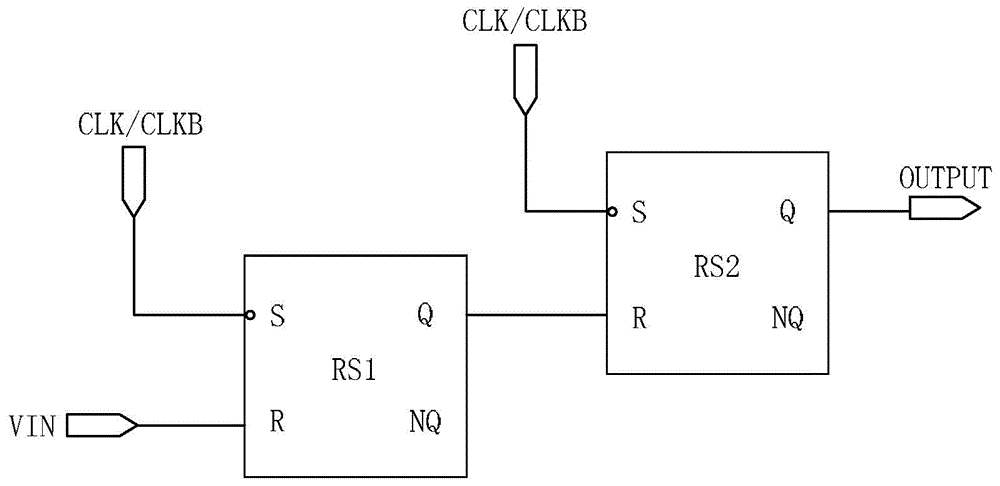

Shifting register unit, gate driving circuit and display device

A technology for shift registers and gates, which is applied in the field of gate drive circuits, display devices, and shift register units, and can solve problems such as decreased stability of GOA circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

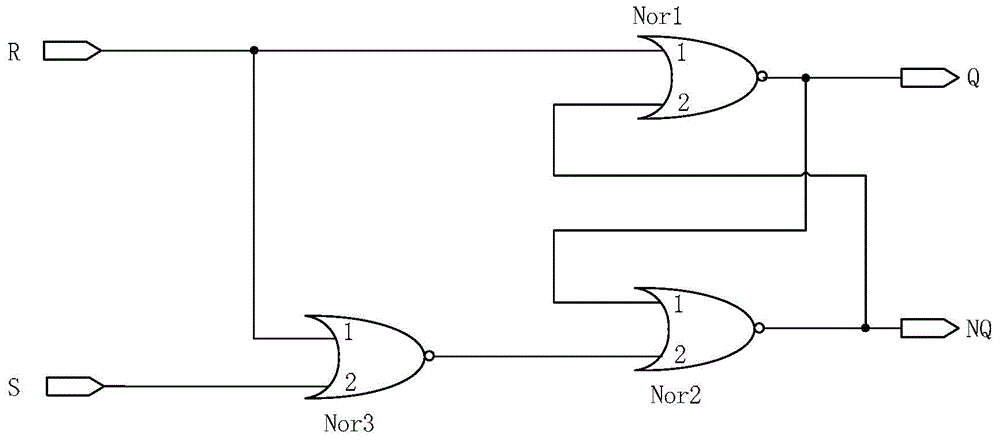

[0037] Such as figure 2 As shown, the first latch module RS1 or the second latch module RS2 may include:

[0038] The first NOR gate nor1, the second NOR gate nor2 and the third NOR gate nor3.

[0039] Wherein, the first input terminal IN1 of the first NOR gate nor1 is used to receive the pulse signal, that is, the first input terminal IN1 of the first NOR gate nor1 can be connected to the first latch module RS1 or the second latch module RS2 The second input terminal R of the first NOR gate nor1; the second input terminal IN2 of the first NOR gate nor1 is connected to the output terminal of the second NOR gate nor2; the output terminal of the first NOR gate nor1 is connected with the first latch module RS1 or the second latch The output terminal Q of the storage module RS2 is connected.

[0040] The first input terminal IN1 of the second NOR gate nor2 is connected to the output terminal of the first NOR gate nor1; the second input terminal IN2 of the second NOR gate nor2 is ...

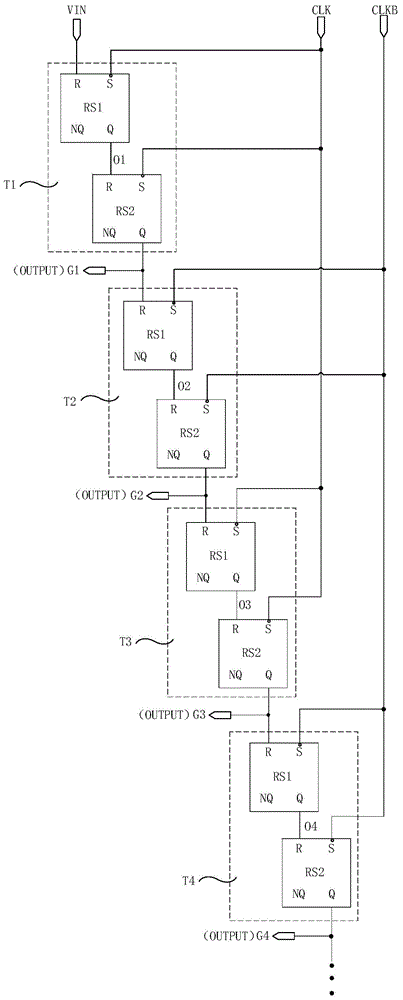

Embodiment 2

[0061] The first NOR gate nor1, the second NOR gate nor2 or the third NOR gate nor3, such as Figure 5 As shown, it may include: a first transistor M1, a second transistor M2, a third transistor M3 and a fourth transistor M4.

[0062] The gate of the first transistor M1 is connected to the first input terminal IN1 of the NOR gate (nor1, nor2 or nor3), the first pole is connected to the first voltage terminal VDDA, and the second pole is connected to the first pole of the second transistor M2 .

[0063] The gate of the second transistor M2 is connected to the second input terminal IN2 of the NOR gate (nor1, nor2 or nor3), and the second pole is connected to the output terminal OUT of the NOR gate;

[0064] The gate of the third transistor M3 is connected to the gate of the second transistor M2, the first pole is connected to the second pole of the second transistor M2, and the second pole is connected to the second voltage terminal GNDA.

[0065] The gate of the fourth transi...

Embodiment 3

[0080] The first NOR gate nor1, the second NOR gate nor2 or the third NOR gate nor3, such as Figure 6 As shown, it may include: a fifth transistor M5, a sixth transistor M6 and a seventh transistor M7.

[0081] Wherein, the gate of the fifth transistor M5 is connected to the first input terminal IN1 of the NOR gate (nor1, nor2 or nor3), the first pole is connected to the output terminal OUT of the NOR gate (nor1, nor2 or nor3), and the second pole is connected to the output terminal OUT of the NOR gate (nor1, nor2 or nor3). The second voltage terminal GNDA is connected to each other.

[0082] The gate of the sixth transistor M6 is connected to the second input terminal IN2 of the NOR gate (nor1, nor2 or nor3), the first pole is connected to the first pole of the fifth transistor M5, and the second pole is connected to the second voltage terminal GNDA. connect.

[0083] The gate and the first pole of the seventh transistor M7 are connected to the first voltage terminal VDDA,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com