Trench MOSFET (Metal Oxide Semiconductor Field Effect Transistor) device and manufacturing method thereof

A manufacturing method and groove technology, which are applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electrical components, etc., can solve the problem of low withstand voltage in the terminal area, and achieve the effect of improving the withstand voltage and improving the withstand voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

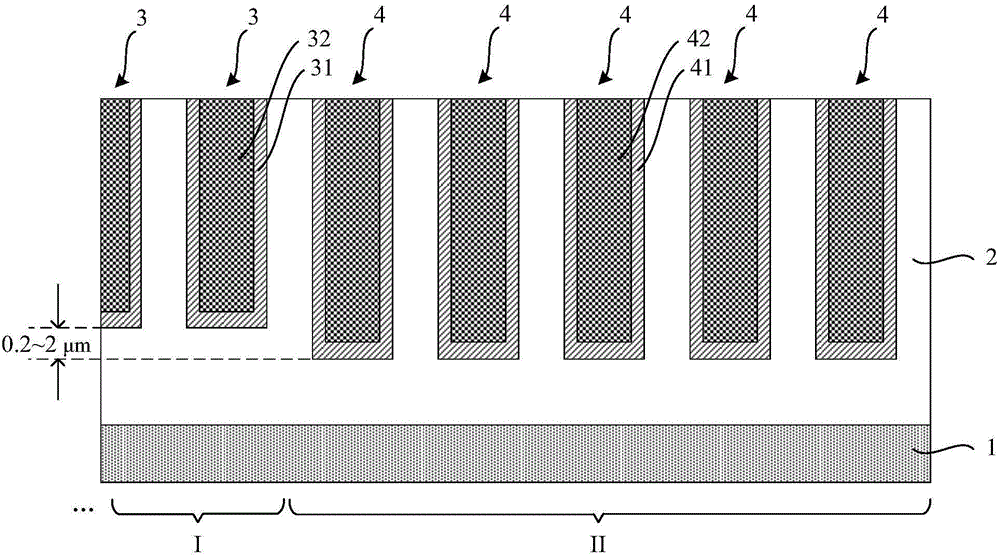

[0072] The present invention provides a trench MOSFET device, please refer to figure 1 , showing a cross-sectional view of the structure of the device, including an N-type heavily doped substrate 1 and an N-type lightly doped epitaxial layer 2 formed on the N-type heavily doped substrate 1; the N-type lightly doped epitaxial layer 2 A plurality of trench structures 3 in the cell region and a plurality of trench structures 4 in the termination region are formed in the layer 2 , wherein the depth of the trench structures 4 in the termination region is greater than the depth of the trench structures 3 in the cell region.

[0073] The cell region trench structure 3 is located in the cell region I of the trench MOSFET device, and the termination region trench structure 4 is located in the termination region II of the trench MOSFET device.

[0074] Specifically, the N-type heavily doped substrate 1 serves as the drain region of the trench MOSFET device, and the N-type lightly doped ...

Embodiment 2

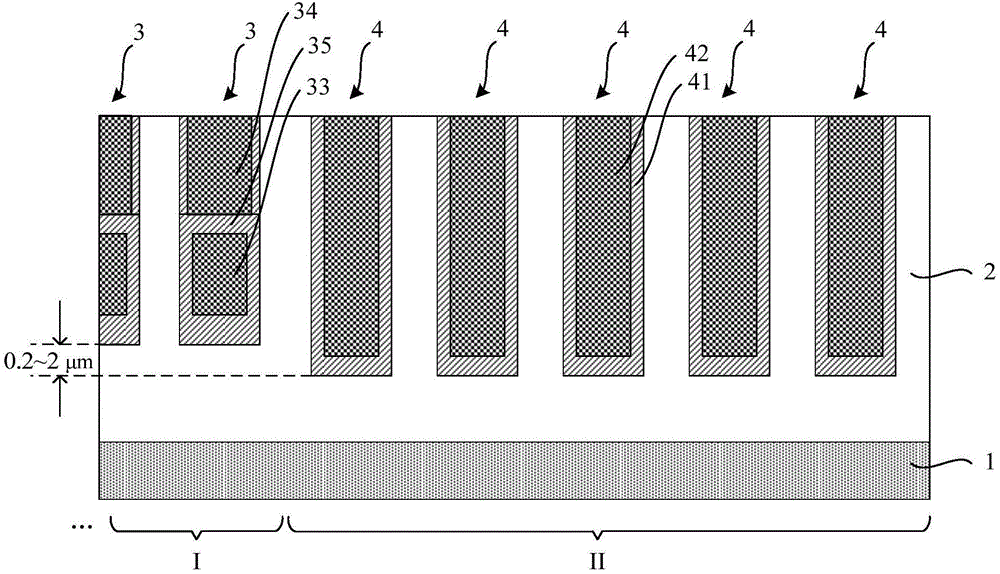

[0080] This embodiment adopts basically the same technical solution as Embodiment 1, the difference is that in Embodiment 1, the trench structure in the cell area adopts a conventional trench gate structure, while in this embodiment, the trench structure in the cell area The structure adopts the split gate structure.

[0081] see figure 2 , showing a cross-sectional view of the structure of a trench MOSFET device in this embodiment, including an N-type heavily doped substrate 1 and an N-type lightly doped epitaxial layer 2 formed on the N-type heavily doped substrate 1; In the N-type lightly doped epitaxial layer 2 are formed a plurality of trench structures 3 in the cell region and a plurality of trench structures 4 in the termination region, wherein: the trench structures 4 in the termination region are deeper than the trench structures 3 in the cell region depth.

[0082] Such as figure 2 As shown, the cell region trench structure 3 is a split gate, including a shieldi...

Embodiment 3

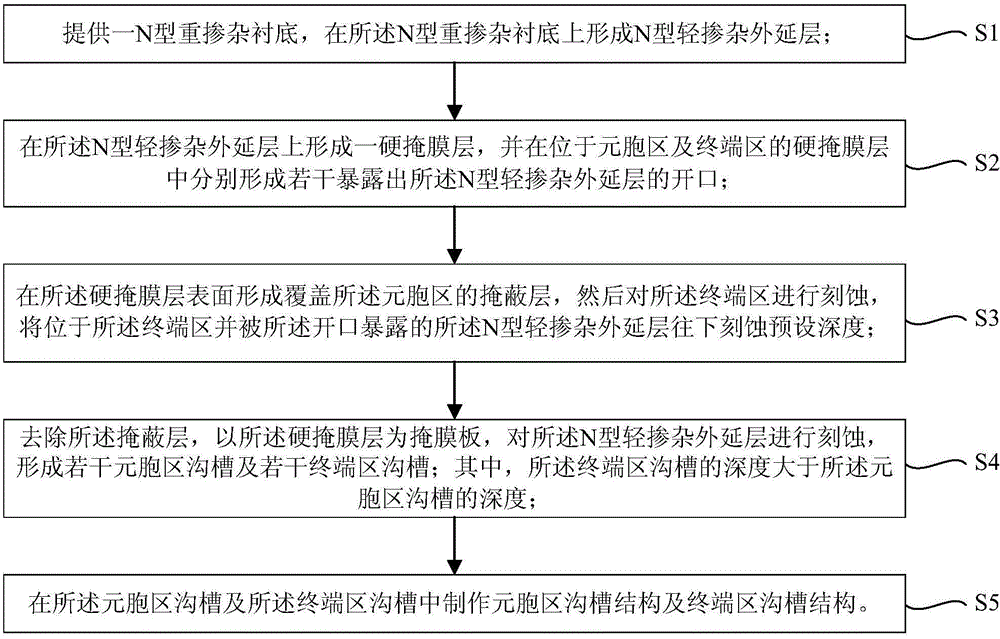

[0086] A kind of fabrication method of trench MOSFET device of the present invention is as follows, please refer to image 3 , shown as a process flow diagram of the method, at least comprising the following steps:

[0087] Step S1: providing an N-type heavily doped substrate, and forming an N-type lightly doped epitaxial layer on the N-type heavily doped substrate;

[0088] Step S2: forming a hard mask layer on the N-type lightly doped epitaxial layer, and forming a number of exposed N-type lightly doped epitaxial layers in the hard mask layer located in the cell region and the terminal region respectively. opening;

[0089] Step S3: Form a masking layer covering the cell region on the surface of the hard mask layer, and then etch the terminal region, and the N-type light located in the terminal region and exposed by the opening The doped epitaxial layer is etched down to a preset depth;

[0090] Step S4: removing the masking layer, using the hard mask layer as a mask, etc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com