An error injection method for nand Flash simulation model with controllable bit flipping

A technology of simulation model and number of digits, which is applied to the detection of faulty computer hardware, static memory, instruments, etc., and can solve problems such as complex operation methods and poor controllability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

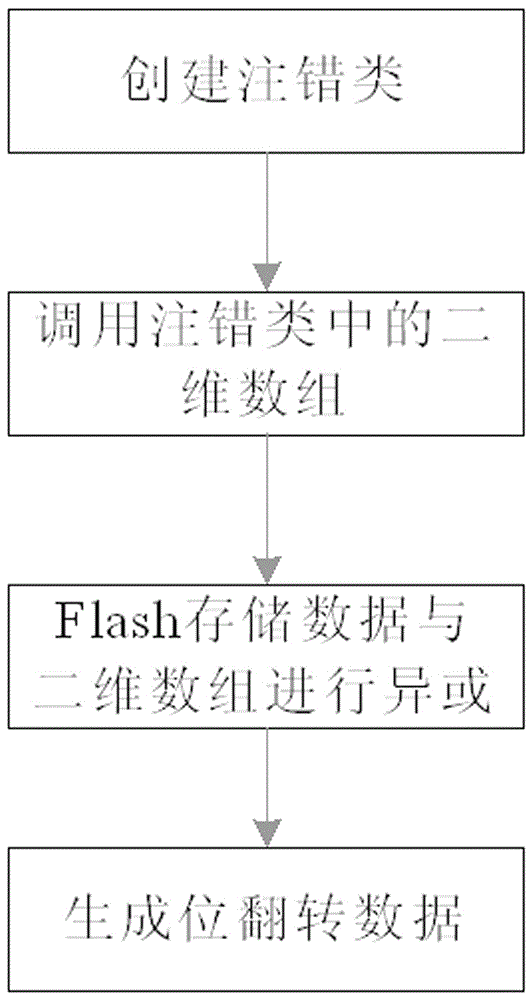

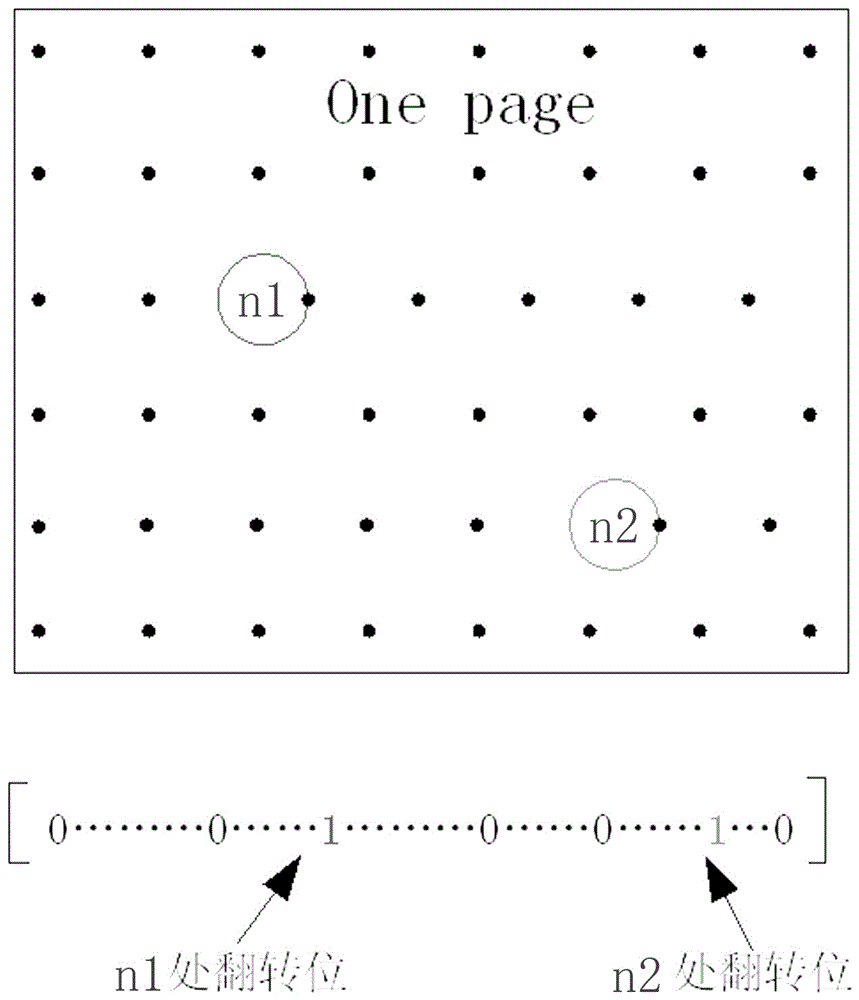

[0014] The wrong note method of the controllable Nand Flash emulation model of bit flipping of the present invention, the page size of setting Nand Flash is bit, the addressing bits of data stored in the Nand Flash page is , the page size of commonly used Nand Flash is 8KB or 16KB, namely bit is equal to bit or bit, the encoding error correction verification method is realized through the following steps:

[0015] a). Determine the type of bit flip, determine whether the number of bit flips is randomly generated or artificially set, if it is randomly generated, then perform step b); if it is artificially set, then perform step c);

[0016] b). Randomly generate the number of bit flips, within the limited bit flip interval Randomly generate a data within, use this random data as the number of bit flips in the Nand Flash page, perform step d); ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com