Method for preparing ONO medium layer

A dielectric layer and bottom layer technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve problems such as uneven distribution, intensified gas distribution, and influence on electrical uniformity, so as to achieve strong realizability and reduce shell Body, improve the effect of thickness uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In the following description, a lot of specific details are given in order to provide a more thorough understanding of the present invention. However, it is obvious to those skilled in the art that the present invention can be implemented without one or more of these details. In other examples, in order to avoid confusion with the present invention, some technical features known in the art are not described.

[0037] In order to thoroughly understand the present invention, detailed steps and detailed structures will be presented in the following description to explain the technical solution of the present invention. The preferred embodiments of the present invention are described in detail as follows. However, in addition to these detailed descriptions, the present invention may also have other embodiments.

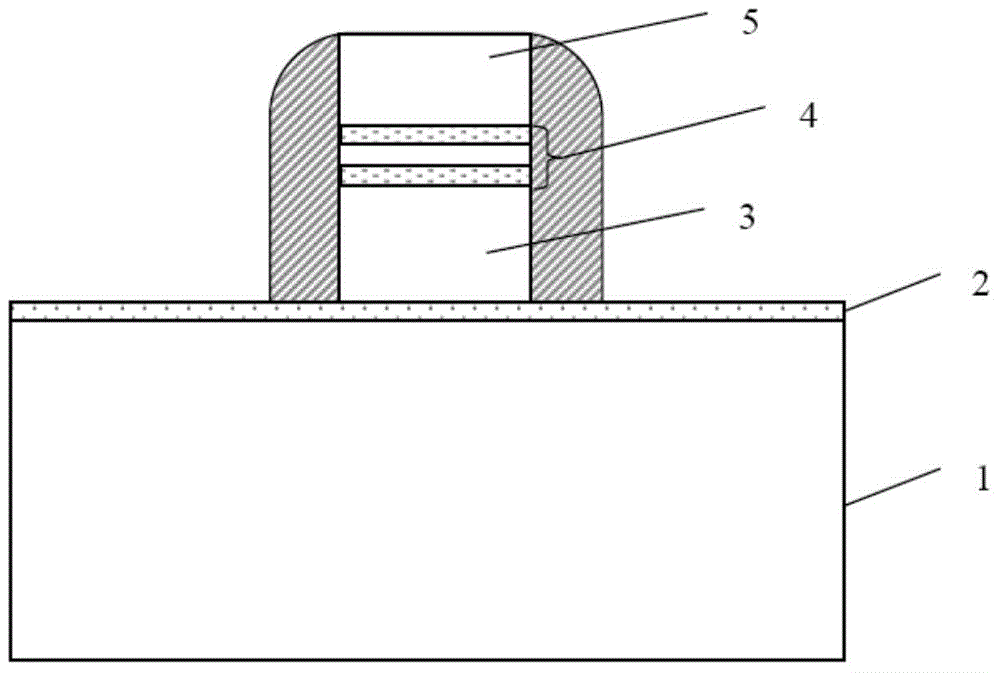

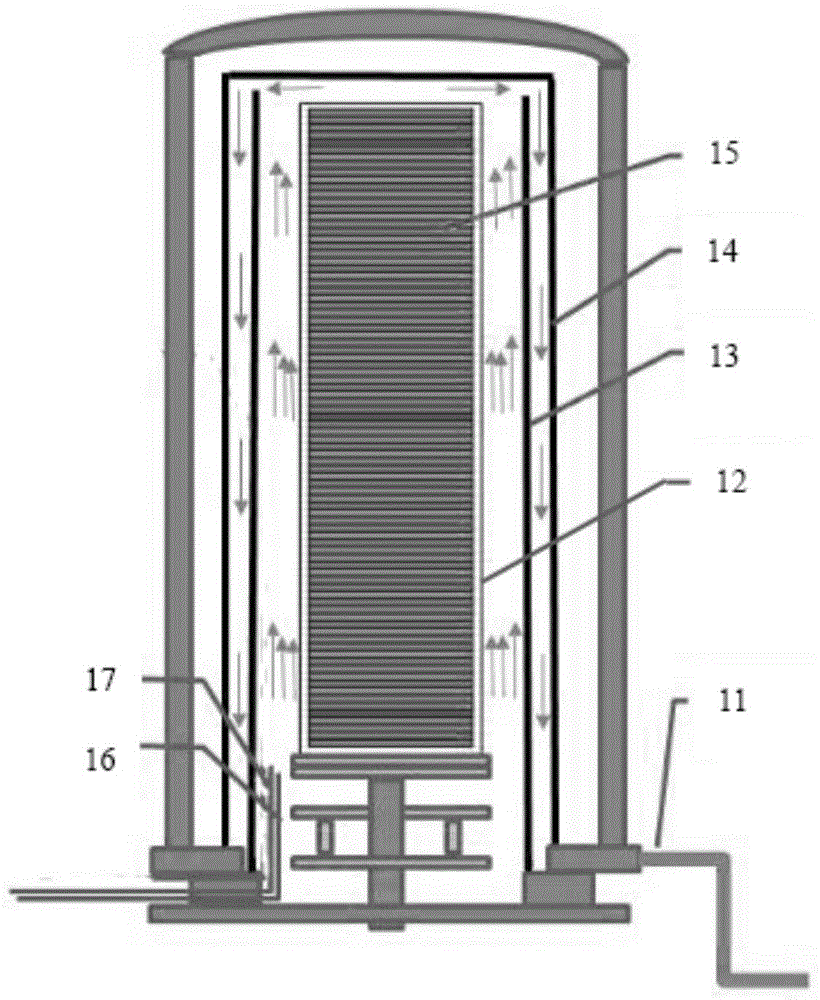

[0038] The present invention provides a method for preparing an ONO dielectric layer, including the following steps: A method for preparing an ONO dielectric layer, su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com