Scan test latch macrocell and scan test method

A technology of scan test and latch, which is applied in the field of scan test macrocell and scan test, can solve the problems of insufficient fault coverage and design complexity, and achieve the goal of reducing test escape rate, low degree of automation and fast operation speed Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

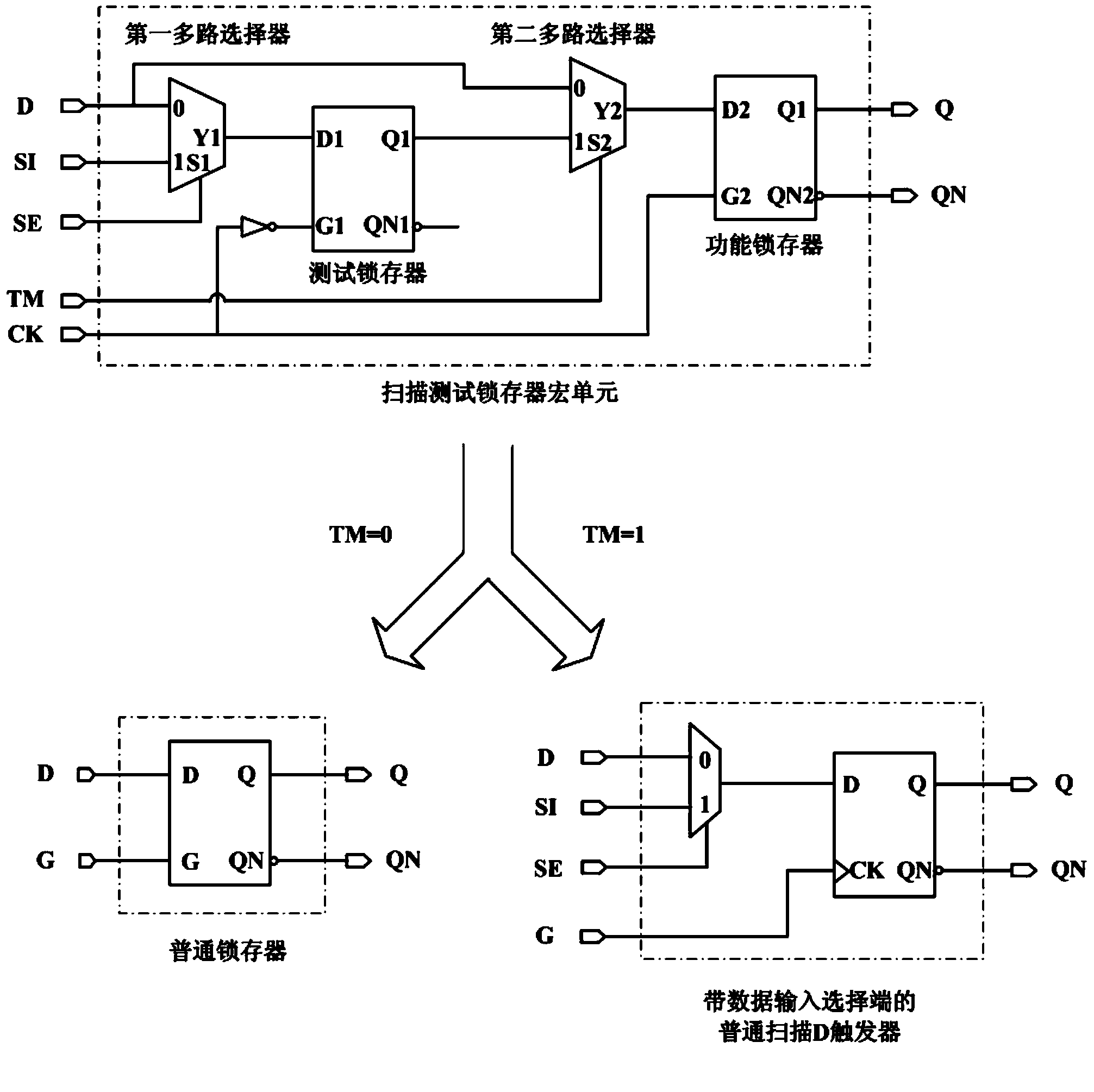

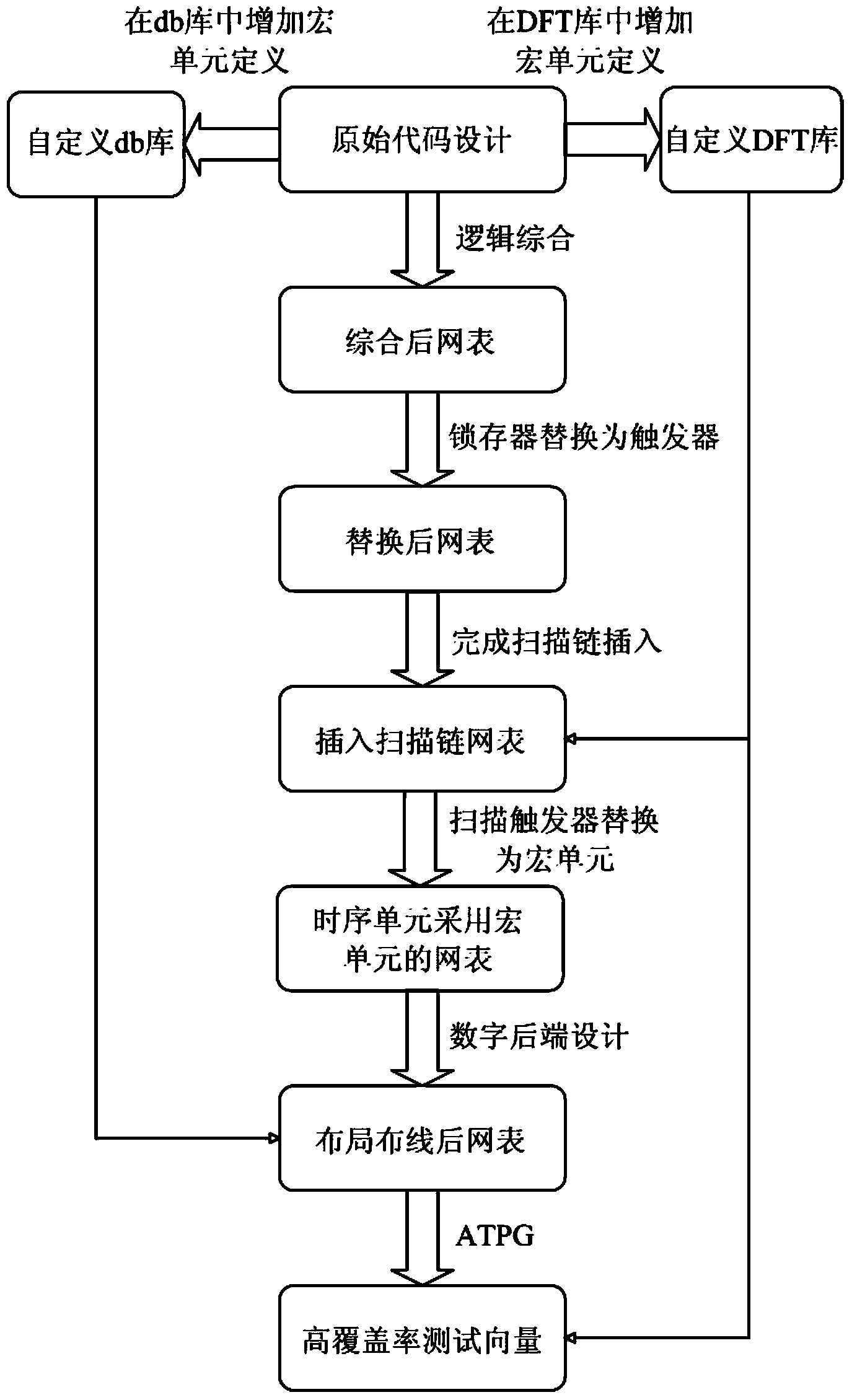

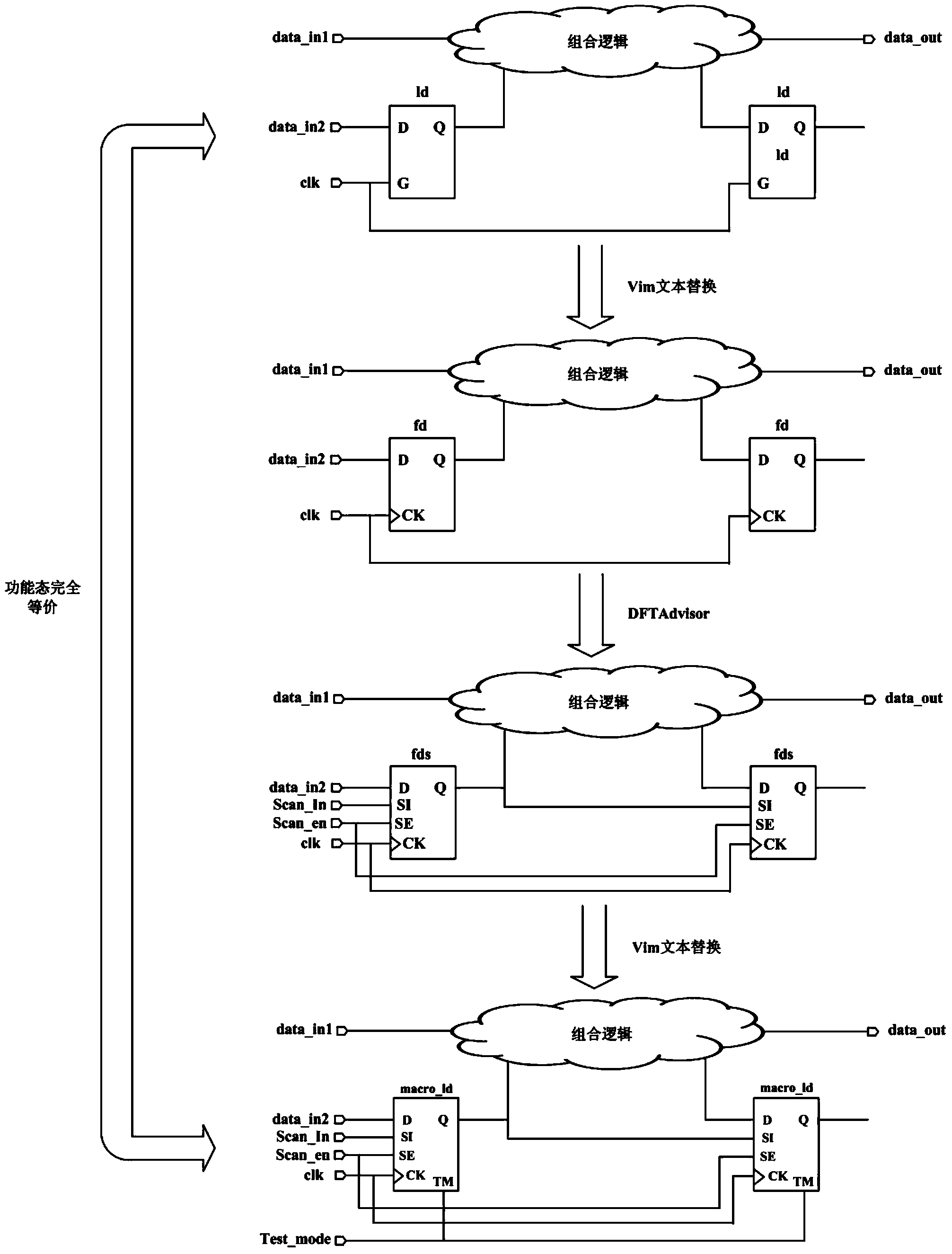

[0037] Such as figure 1 As shown, the realization process of the present invention is first to define the equivalent scan test macrocell model of a common latch unit, it is characterized in that comprising: two latches, an inverter and two multiplexers;

[0038] The two latches are respectively a test latch and a functional latch; the two multiplexers are respectively a first multiplexer and a second multiplexer;

[0039] The 0 data input port (i.e. the first data input port) of the first multiplexer is connected with the data port D, the 1 data input port (i.e. the second data input port) is connected with the scanning input port SI of the macrocell, and the input port is selected S1 is connected to the scan enable port SE of the macrocell, and the data output port Y1 is connected to the input port D1 of the test latch;

[0040] The input port of the inverter is connected to the clock input port CK of the macro unit, and the output port is connected to the latch control sign...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com