Voltage level switching circuit

A technology for converting circuits and voltage levels, which is applied in the direction of logic circuit connection/interface layout, etc., can solve the problems of difficult transition, circuit leakage, and increased power consumption, so as to shorten the rise and fall time, reduce the circuit area, and save costs. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] Below in conjunction with accompanying drawing and embodiment the present invention is described in detail:

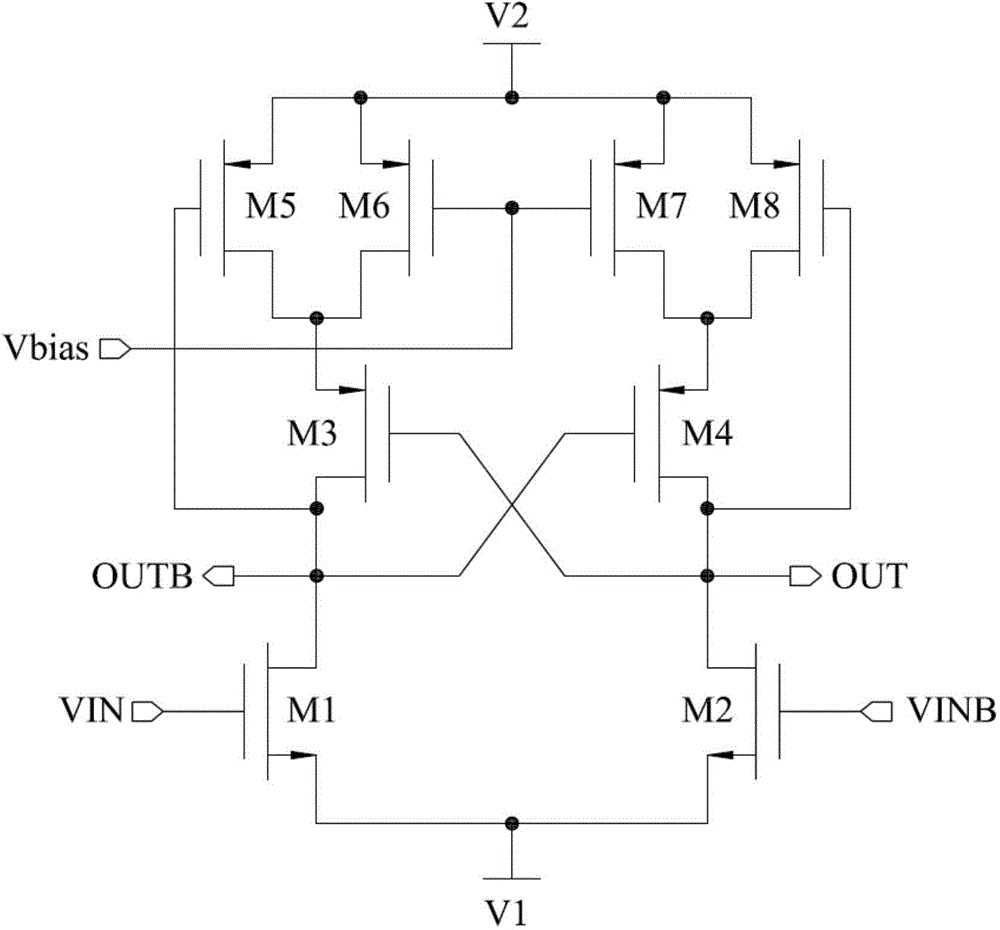

[0046] refer to image 3 , The first preferred embodiment of the voltage level conversion circuit of the present invention includes a first output terminal OUT and a second output terminal OUTB, a first transistor M1, a second transistor M2, a third transistor M3, a first Four transistors M4, a fifth transistor M5, a sixth transistor M6, a seventh transistor M7, an eighth transistor M8, and a bias input terminal Vbias.

[0047] The first output terminal OUT and the second output terminal OUTB are respectively used to output a first output voltage and a second output voltage complementary to the first output voltage.

[0048] The first transistor M1 includes a first terminal electrically connected to the second output terminal OUTB, a second terminal electrically connected to a first level voltage V1, and a control terminal receiving a first input voltage VIN. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com