Low noise amplifier

A low-noise amplifier and amplifier technology, applied in the direction of improving the amplifier to reduce the influence of noise, etc., can solve the problem of inability to further improve the gain, and achieve the effects of low cost, improved gain performance, and increased high-frequency gain.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

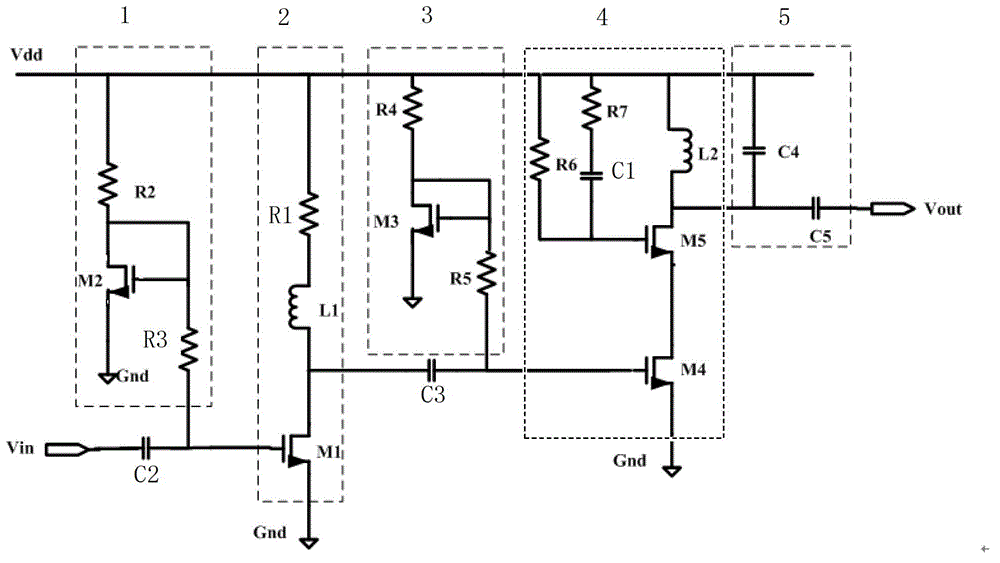

[0019] Such as figure 2 Shown is the structure diagram of the low noise amplifier of the embodiment of the present invention. The low noise amplifier in the embodiment of the present invention includes: a cascaded first-stage amplifying circuit 2 and a second-stage amplifying circuit 4 , a first-stage bias circuit 1 , a second-stage bias circuit 3 , and an output impedance matching circuit 5 .

[0020] The first-stage amplifying circuit 2 includes a first NMOS transistor M1 connected to a common source, the source of the first NMOS transistor M1 is grounded Gnd, and the drain of the first NMOS transistor M1 is connected in series with the power supply voltage Vdd. There is a first resistor R1 and a first inductor L1, the first stage bias circuit 1 provides a first bias voltage to the gate of the first NMOS transistor M1, the gate of the first NMOS transistor M1 is the The input end of the first-stage amplifying circuit 2, the drain of the first NMOS transistor M1 is used as ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com