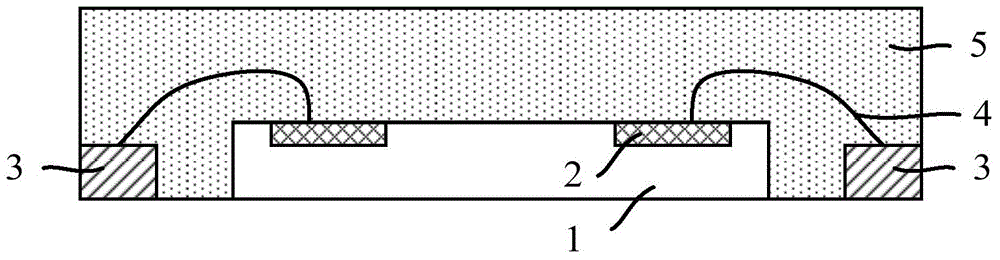

Semiconductor packaging structure

A packaging structure and semiconductor technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., can solve the problems of increasing or unfavorable packaging structure integration, large volume, etc., to achieve increased integration and reduced area , small size effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

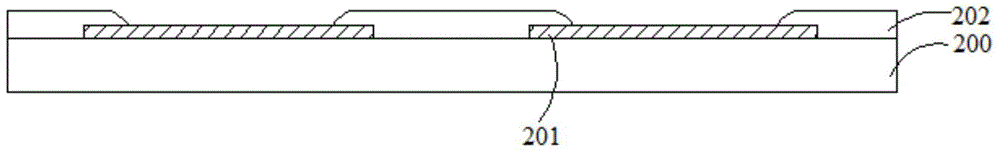

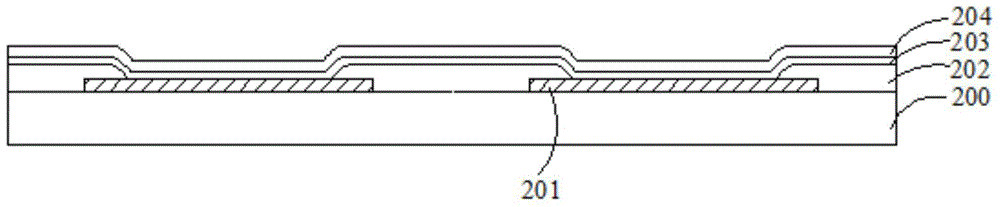

[0012] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0013] First, refer to figure 2 , provide a semiconductor chip 200, the surface of the semiconductor chip 200 is provided with a bonding pad 201 and a passivation layer 202, and the passivation layer 202 is provided with a first opening exposing the bonding pad 201.

[0014] The pad 201 is the functional output terminal of the chip 200, and finally realizes the conductive transition of the electrical function through the post-formed stud bump 206; the material of the passivation layer 202 includes silicon oxide, silicon nitride, silicon oxynitride, poly Dielectric materials such as imide and benzenetributene or their mixtures are used to protect the circuits in the chip 200 .

[0015] It should be noted that the pad and passivation layer of the chip can be the initial pad and the initial passivation layer of the chip, and can also be a t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com