A multi-physical domain collaborative design method for three-dimensional integrated circuits based on through-silicon vias

An integrated circuit and collaborative design technology, which is applied in the direction of electrical digital data processing, calculation, and special data processing applications, can solve the problems of not considering the influence of reliability, spending a lot of money, and increasing the cost of three-dimensional integrated circuit design, so as to improve Design efficiency, reduce design complexity, and reduce design cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

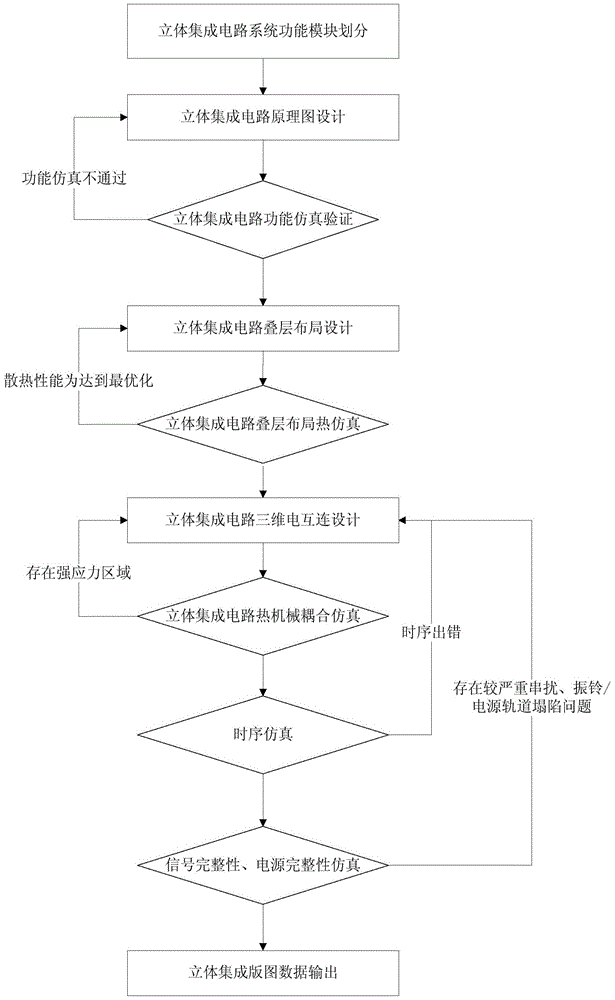

Method used

Image

Examples

Embodiment 1

[0082] According to the design method proposed by the present invention, the three-dimensionally integrated 4M SRAM memory design steps are as follows:

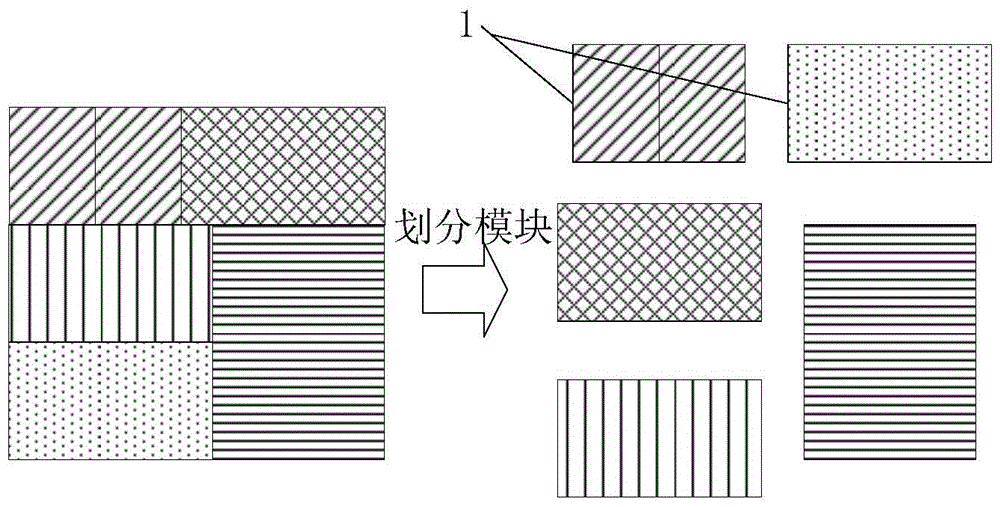

[0083] 1) Three-dimensional integrated 4M SRAM memory system functional module division

[0084] The 4M SRAM memory system can be divided into four independent 1M SRAM memory sub-modules according to functions, and one 1M SRAM memory is arranged on a chip layer, a total of 4 layers.

[0085] 2) Schematic design of three-dimensional integrated 4M SRAM memory

[0086] Use Altium Designer software to draw four 1M SRAM memory two-dimensional circuit schematic diagrams. At this time, the TSV delay characteristics are not introduced into the interconnection relationship of each 1M SRAM in the schematic diagram.

[0087] Three-dimensional integrated 4M SRAM memory function simulation verification: Input the RTL code of the above schematic diagram into ModelSim or Incisive software, and verify whether all functions are correct throu...

Embodiment 2

[0104] According to the design method proposed by the present invention, the design steps of a certain three-dimensional integrated electronic system are as follows:

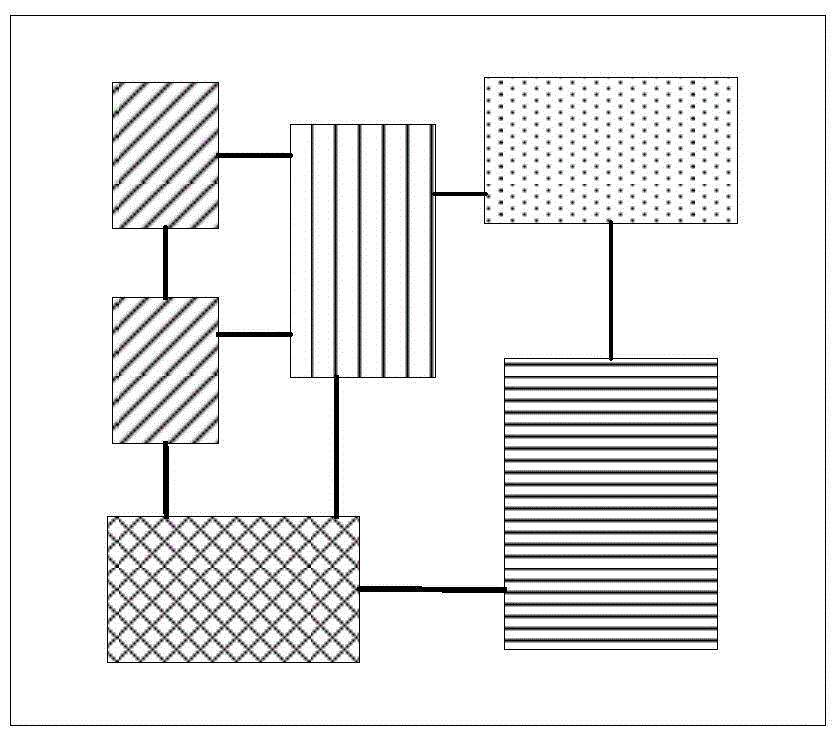

[0105] 1) Division of functional modules of the three-dimensional integrated electronic system

[0106] The three-dimensional integrated electronic system can be divided into SoC modules, various peripheral storage modules and bus modules according to functions. Specifically, there are 5 sub-modules including SoC, CAN bus, SRAM, FLASH, and FPGA.

[0107] 2) Schematic design of three-dimensional integrated electronic system

[0108] Use Altium Designer software to draw a two-dimensional circuit schematic diagram of the electronic system composed of the above five sub-modules. At this time, the interconnection relationship between the five sub-modules in the schematic diagram does not introduce the delay characteristic of through-silicon vias.

[0109] Input the RTL code of the above schematic diagram into Model...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com