Task mapping method for optimizing whole of on-chip network with acceleration nodes

An on-chip network and acceleration node technology, which is applied in inter-program communication, instruments, multi-programming devices, etc., can solve the problem of on-chip network bandwidth reduction and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The present invention will be further analyzed below in conjunction with the accompanying drawings and specific embodiments.

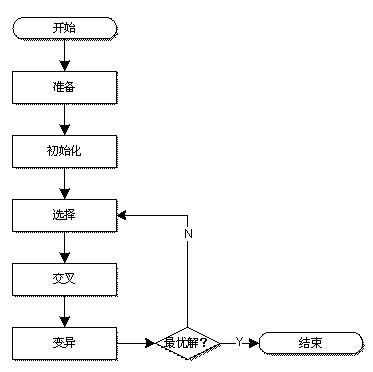

[0040] Such as figure 1 Shown, the inventive method comprises the following steps:

[0041] Step (1). Preparation stage

[0042] 1.1 Accumulate the communication traffic of any two subtasks in advance to obtain the communication traffic between each pair of subtasks.

[0043] 1.2 Determine the range of feasible solutions for subtasks

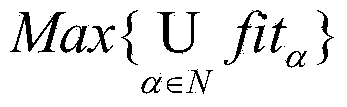

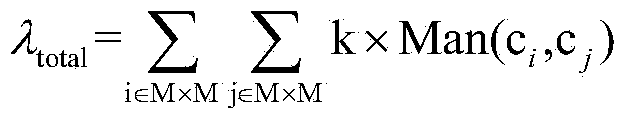

[0044] The present invention assumes that the amount of communication between m subtasks is 1, and then maps these subtasks on n processors; since the amount of communication between subtasks is set to 1, the overall calculation amount is very small , can be quickly solved by enumeration to obtain the region with the optimal feasible solution range of the subtask; the optimal region is the set of mapping layouts with the best fitness, as can be seen from formula (1):

[0045] Max { ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com