Dual-axis tensile strain GeSn n channel tunneling field effect transistor

A tunneling field effect and transistor technology, which is applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of poor material quality and thermal stability, difficulties, etc., and achieve the effect of increasing tunneling current and improving device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to understand the technical essence of the present invention more clearly, the structure and process realization of the present invention are described in detail below in conjunction with the accompanying drawings and embodiments:

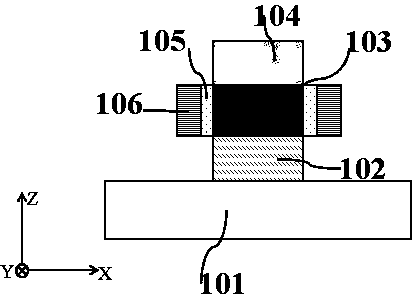

[0019] see figure 1 The biaxial tensile strained GeSn n-channel tunneling field effect transistor is shown, which includes:

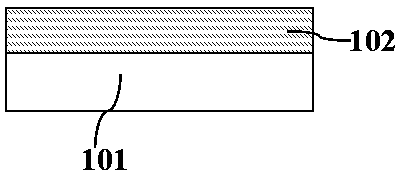

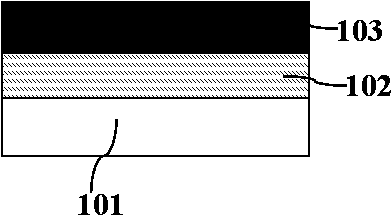

[0020] A substrate 101, the material is single crystal Ge;

[0021] One n channel 103, the material is single crystal GeSn, the general formula is Ge 1-x sn x (0≤ y ≤0.25), if using Ge 0.95 sn 0.05 ;

[0022] A source 102, the material is single crystal GeSn, the general formula is Ge 1-y sn y (0x ≤0.25, x > y ) If Ge can be used 0.9 sn 0.1

[0023] An insulating dielectric film 105 is grown on the channel, such as using H-k (high-k value) material hafnium dioxide H f o 2;

[0024] a gate electrode 106 covering the insulating dielectric film;

[0025] A drain electrode 104 is made of single ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com