A semiconductor device with an improved packaging structure and its manufacturing method

A packaging structure, semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as affecting the on-resistance of devices, reduce parasitic inductance, increase contact area, and fusing current. increased effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

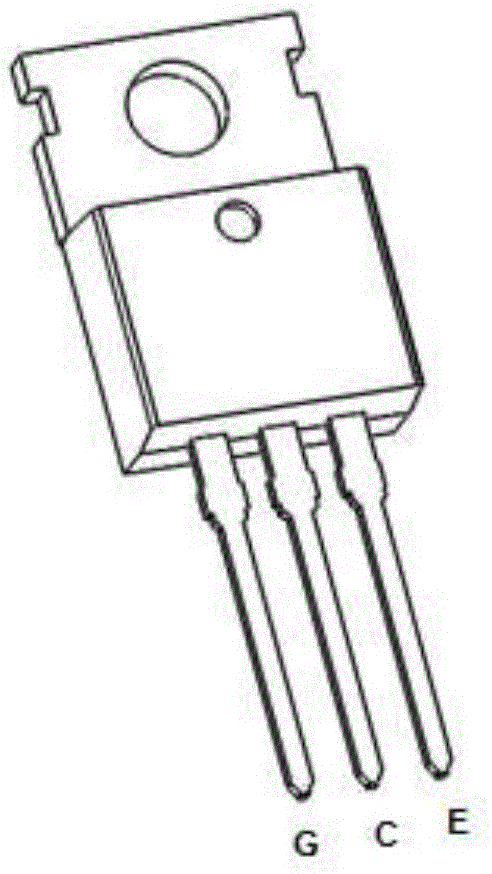

[0064] Such as image 3 As shown, on the three-dimensional perspective view of the semiconductor device, it includes a MOSFET chip, a TO-220 lead frame and a TO-220 packaging resin. The MOSFET chip has two corresponding main surfaces, namely a first main surface and a second main surface, wherein the first main surface has a gate and a source of the MOSFET chip, and the source area is much larger than the gate area, There is a drain electrode of a MOSFET chip on the second main surface; the TO-220 lead frame includes a frame body area located at the top of the lead frame, a carrier base island area at the middle of the lead frame, and a pin area at the bottom of the lead frame, three areas connected to each other; the second main surface of the MOSFET chip is adhesively mounted on the base island area of the carrier; the pin area includes a first pin, a second pin and a third pin, and the second pin The pin is located in the middle of the first pin and the third pin; the to...

Embodiment 2

[0066] Such as Figure 4 As shown, on the three-dimensional perspective view of the semiconductor device, it includes a MOSFET chip, a TO-263 lead frame and a TO-263 packaging resin. The MOSFET chip has two corresponding main surfaces, namely a first main surface and a second main surface, wherein the first main surface has a gate and a source of the MOSFET chip, and the source area is much larger than the gate area, There is a drain electrode of a MOSFET chip on the second main surface; the TO-263 lead frame includes a frame body area located at the top of the lead frame, a carrier base island area at the middle of the lead frame, and a pin area at the bottom of the lead frame, three areas connected to each other; the second main surface of the MOSFET chip is adhesively mounted on the base island area of the carrier; the pin area includes a first pin, a second pin and a third pin, and the second pin The pin is located in the middle of the first pin and the third pin; the t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com