Addressable test chip and test method thereof

A testing method and addressing technology, applied in semiconductor/solid-state device testing/measurement, electronic circuit testing, electrical components, etc., can solve the problems of small area utilization, inability to detect multiple layers, etc., achieving reduced area and high stability , Improve the effect of defect detection ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

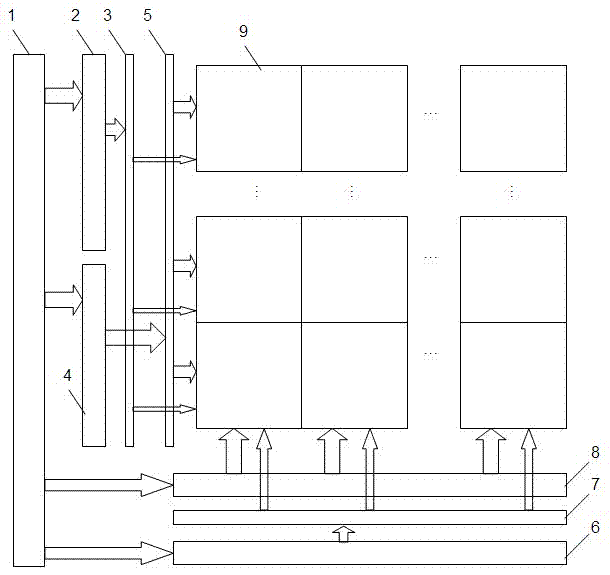

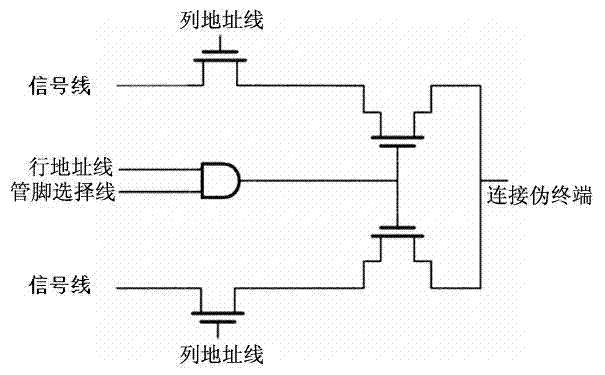

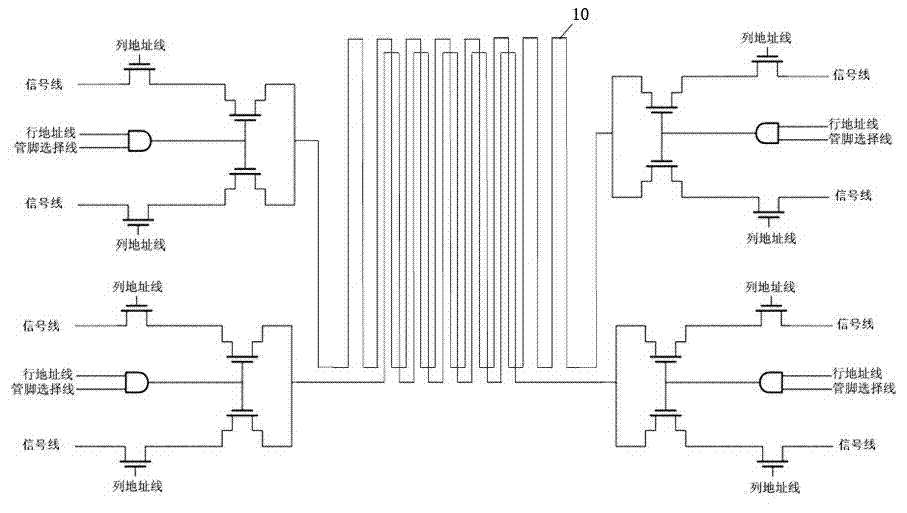

[0030] Embodiment: An addressable test chip of this embodiment includes an addressable circuit, several test frames arranged in an array, and several test structure groups corresponding to the test frames one by one. The test structure groups are placed in In the middle of the test frame. The array formed by the test framework has at least 2 in both the number of rows and the number of columns. Addressable circuits include peripheral address decoding circuits and several switching circuits. Such as figure 1 As shown, the peripheral address decoding circuit includes a row address decoding circuit, a column address decoding circuit and a pin selection decoding circuit. All decoding circuits adopt a two-level decoding structure. The row address decoding circuit includes a row address pre-decoder 2 and a row address secondary decoder 3, and the column address decoding circuit includes a column address pre-decoder 6 and a column address secondary decoder 7, and pin selection dec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com