Three-dimensional laminated semiconductor structure and manufacturing method thereof

A manufacturing method and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as lowering resistance, failure to operate smoothly, and influence on reading speed of three-dimensional stacked flash memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

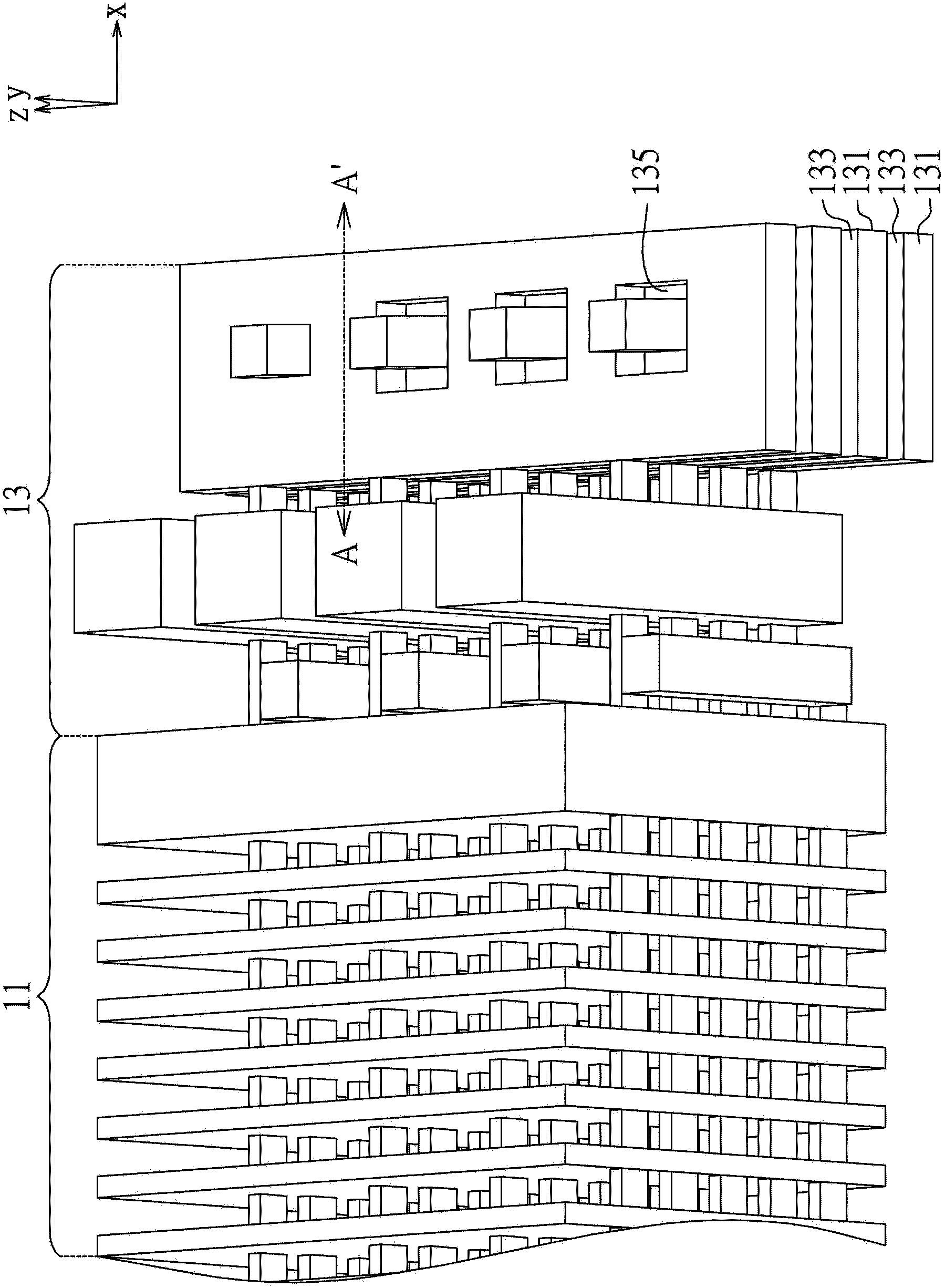

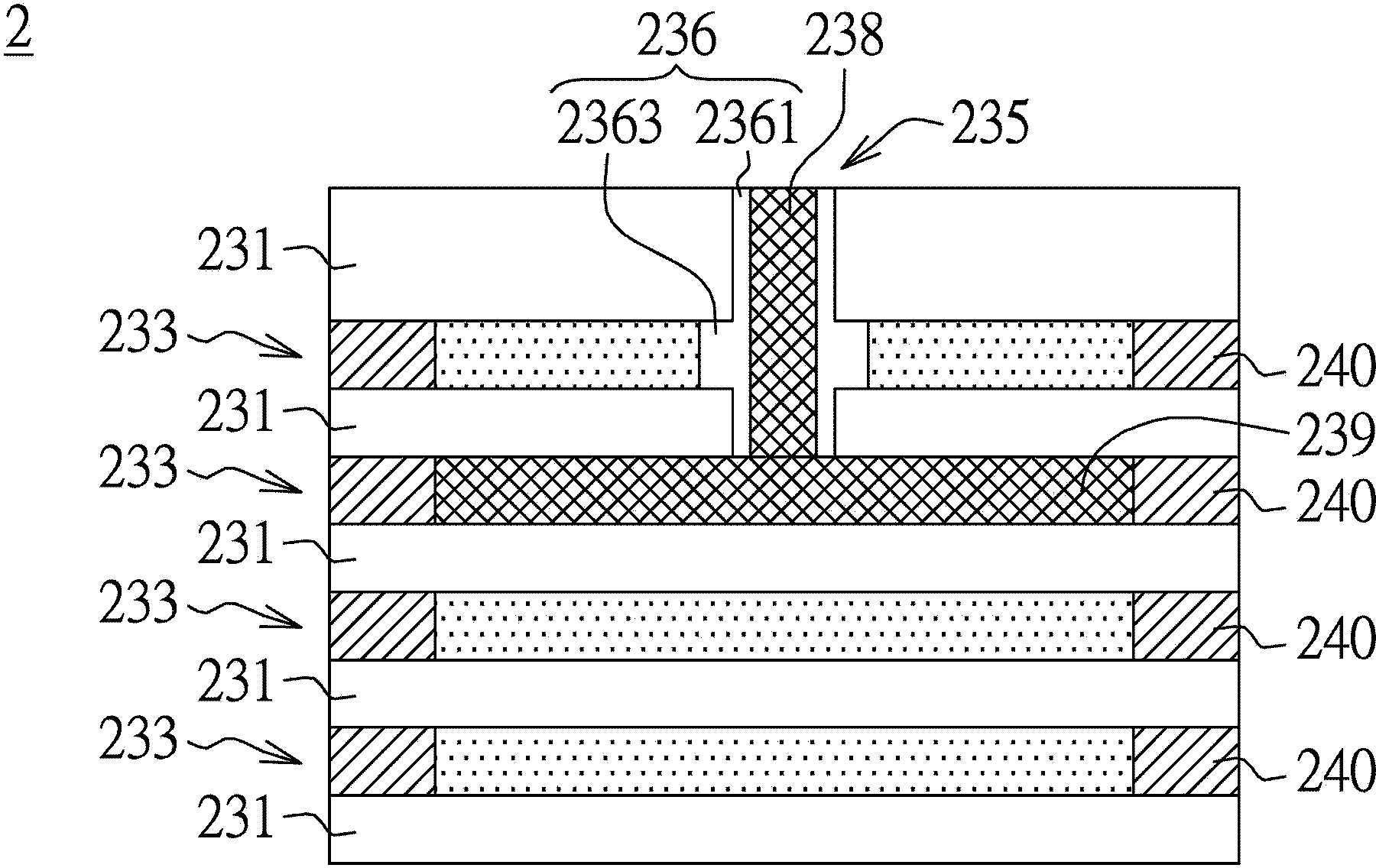

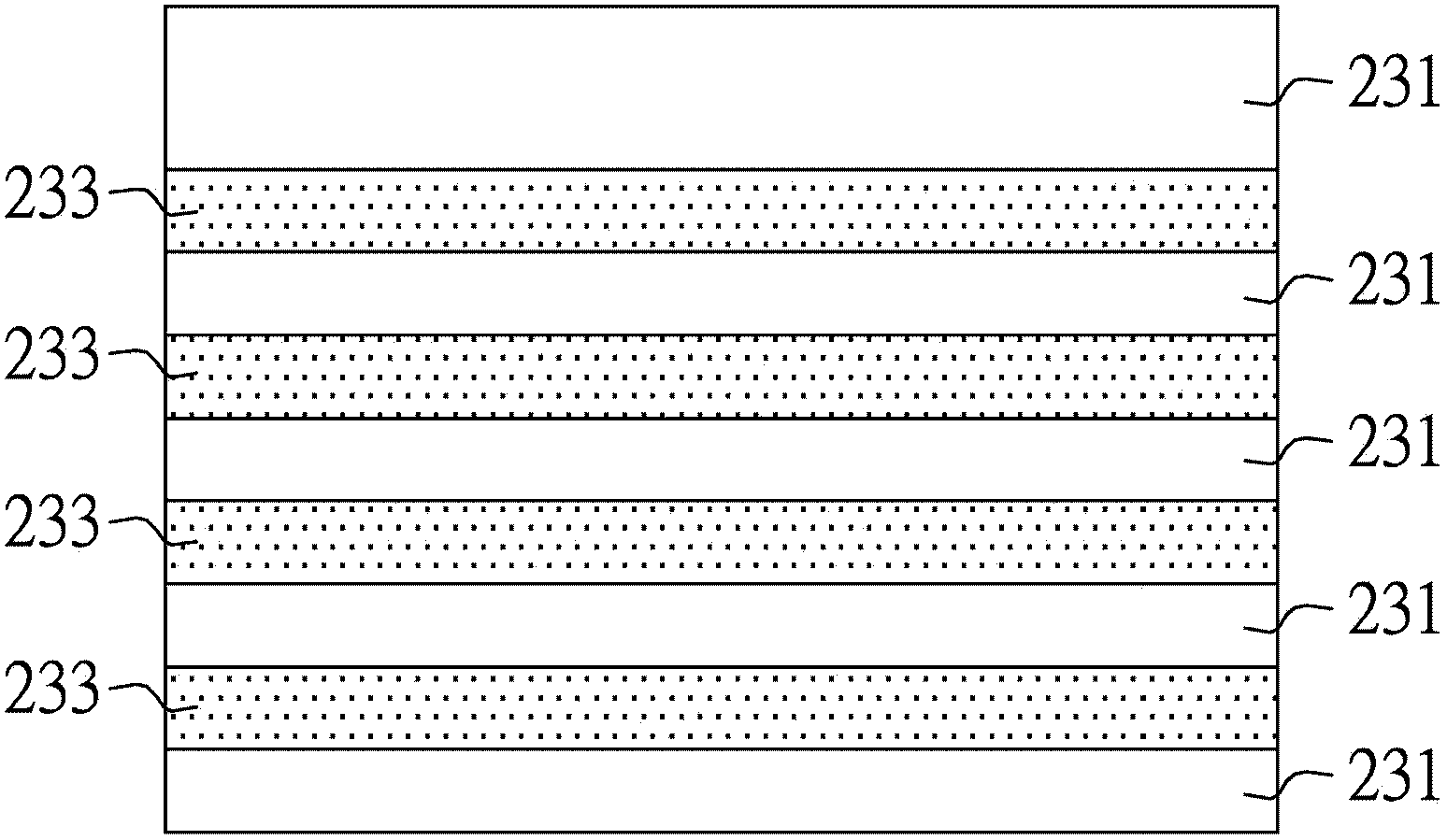

[0035] In embodiments of this disclosure, three-dimensional stacked semiconductor structures and related fabrication methods are presented. The three-dimensional stacked semiconductor structure proposed in the embodiment can reduce the resistance value of the structure without the time-consuming and expensive multi-channel ion implantation process, especially the resistance value of the bit line through which the operating current passes, and greatly accelerate the three-dimensional fast application. Flash memory read speed. Therefore, the embodiment not only has low manufacturing cost through fast process steps, but also enables the application memory to have stable and faster operation performance as a whole.

[0036] Related embodiments are provided below to describe in detail the three-dimensional stacked semiconductor structure proposed by the present invention and the related manufacturing method. However, the descriptions in the embodiments, such as detailed structures...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com