Non-overlapping clock generation circuit

A clock generation circuit, non-overlapping technology, applied in the direction of electric pulse generator circuit, etc., can solve the problems of data error, signal axis interference, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

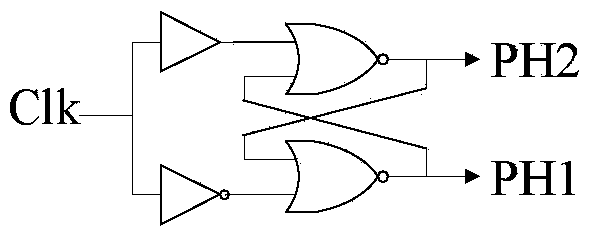

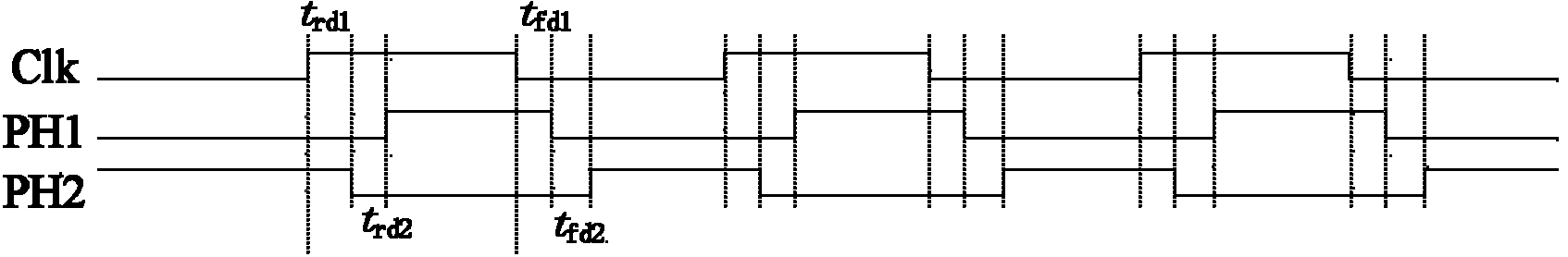

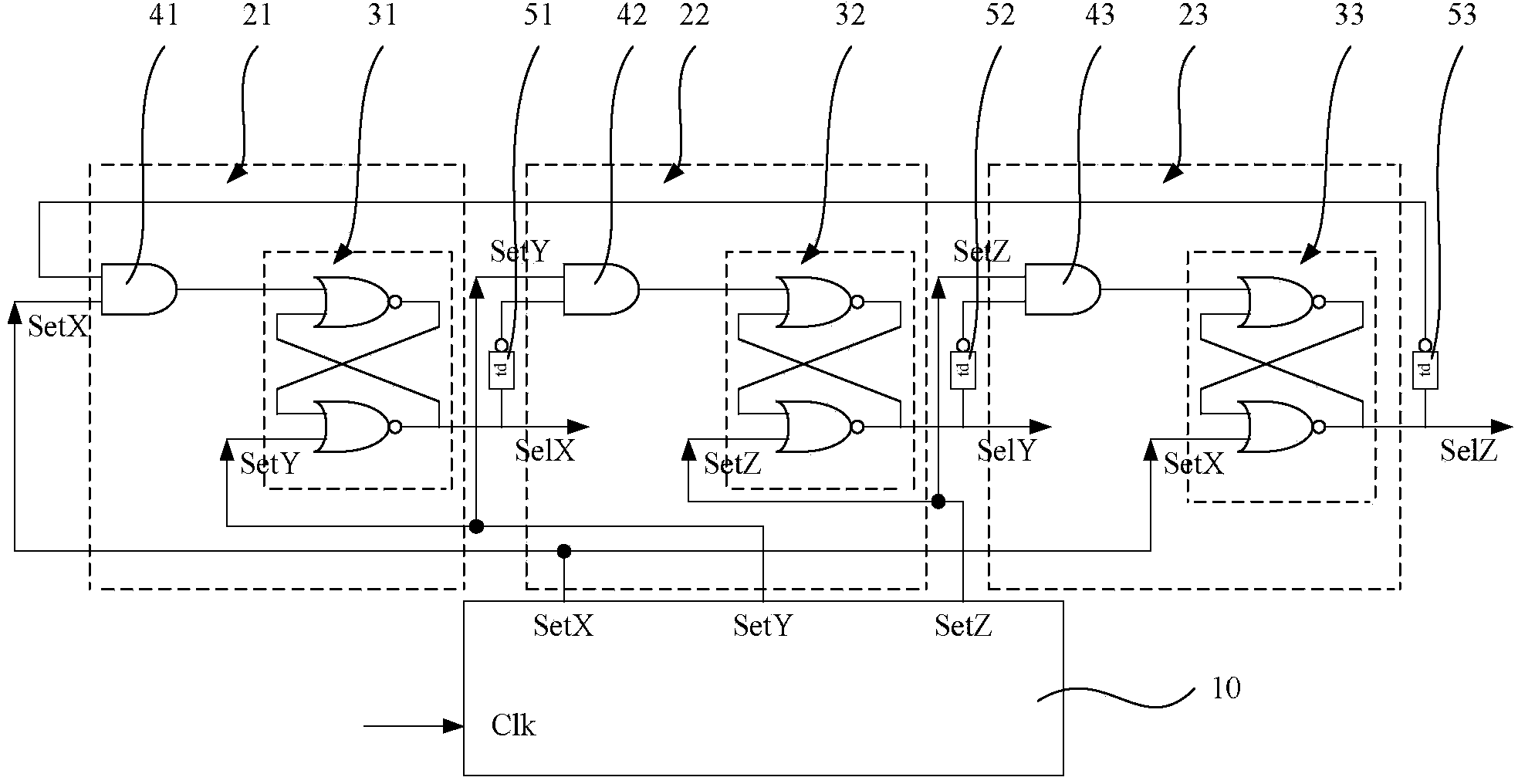

[0029] In the first embodiment, the non-overlapping clock generation circuit can generate three non-overlapping clocks. For details, please refer to image 3 and Figure 4 ,in, image 3 is a schematic diagram of a non-overlapping clock generation circuit according to an embodiment of the present invention; Figure 4 It is a timing diagram of three-phase non-overlapping clocks generated by the non-overlapping clock generation circuit of the embodiment of the present invention.

[0030] Such as image 3 As shown, in this embodiment, the non-overlapping clock generation circuit includes: a finite state machine 10 and three trigger circuits connected to the finite state machine 10;

[0031] The finite state machine 10 can sequentially generate three driving clocks according to the basic clock Clk, which are respectively the first driving clock SetX, the second driving clock SetY and the third driving clock SetZ;

[0032] The 3 trigger circuits are respectively a first trigger ...

Embodiment 2

[0044] Please refer to Figure 5 and Figure 6 ,in, Figure 5 It is a schematic diagram of connection of n trigger circuits in Embodiment 2 of the present invention; Figure 6 It is a schematic diagram of a finite state machine generating n driving clocks according to Embodiment 2 of the present invention. Here, for the sake of illustration clarity, the n trigger circuits and the finite state machine are divided into two diagrams for illustration, specifically, Figure 6 The generated drive clock is supplied to the Figure 5 The set or reset terminals shown, for example, Figure 6 The first driving clock Setφ shown in 1 respectively provided to the set end of the first flip-flop in the first flip-flop circuit 61 and the reset end of the nth flip-flop in the nth flip-flop circuit 6n.

[0045] According to the above three-phase non-overlapping clock generating circuit and Figure 5 and Figure 6 It can be seen that when it is necessary to generate n-phase non-overlapping...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com