Formation of a layout structure for ultra-high withstand voltage resistors

A layout structure, high withstand voltage technology, applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problem of not being able to provide withstand voltage, and achieve the effect of solving insufficient withstand voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

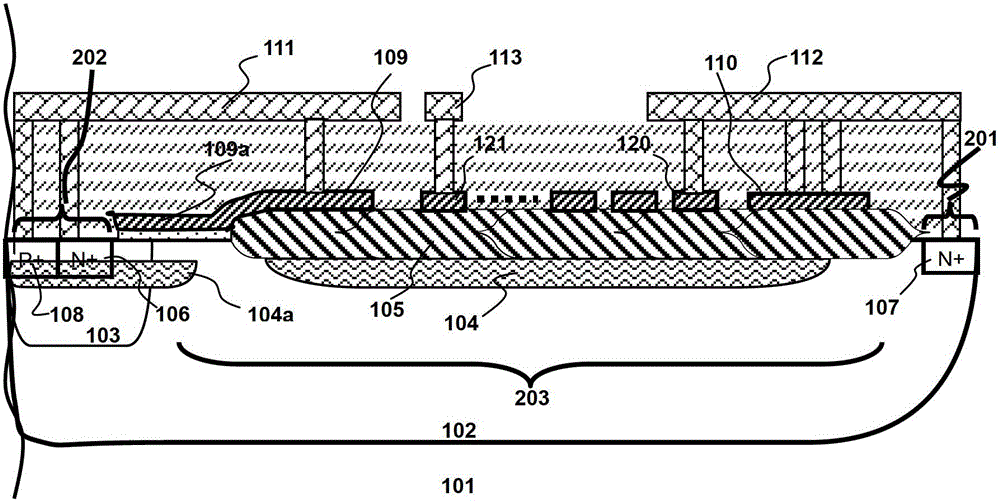

[0018] The layout structure for forming an ultra-high voltage resistance provided by the present invention takes an N-type high voltage field effect transistor as an example, including a circular N-type high voltage field effect transistor and a spiral polysilicon resistor;

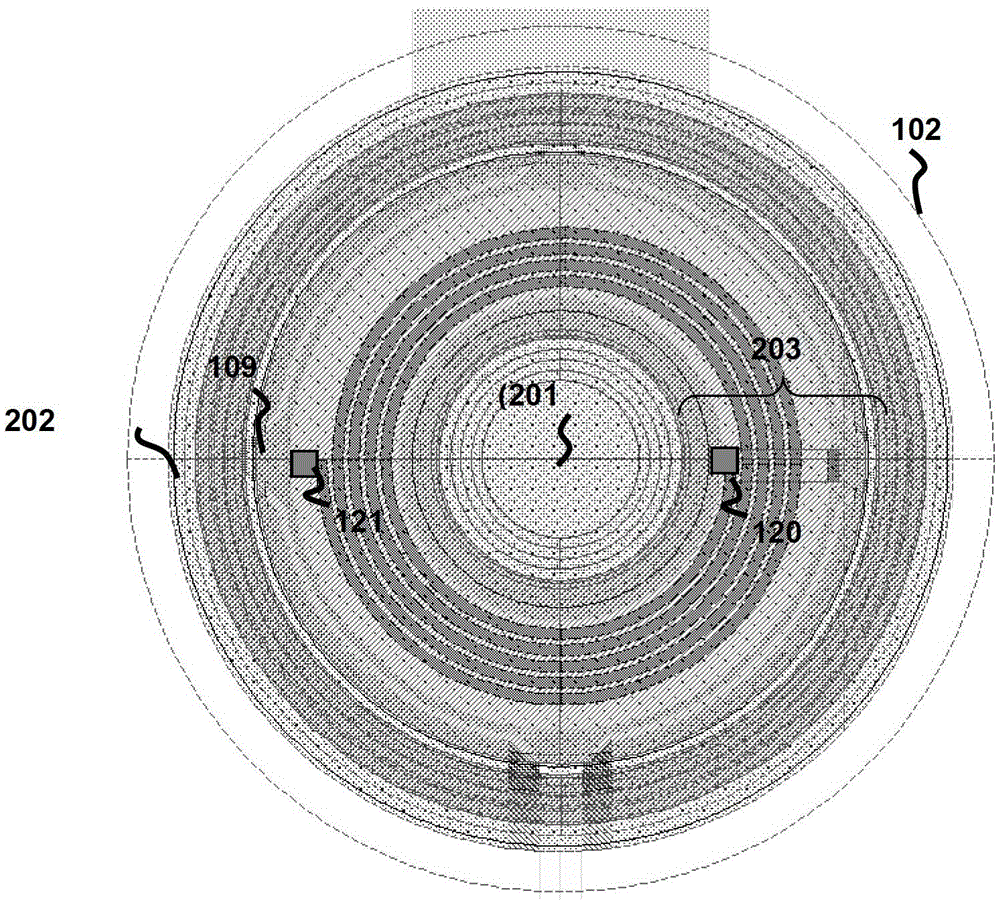

[0019] Such as figure 2 As shown, the N-type high withstand voltage field effect transistor includes a drain region 201, a source region 202, an N-type drain region drift region 203 and an N-type drift region 102; the N-type drift region 102 is located on a P-type silicon substrate 101, The drain region 201, the source region 202 and the N-type drain region drift region 203 are located in the N-type drift region 102; the drain region 201 is located in the center of the field effect transistor, and the N-type drain region drift region 102 is located between the d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com