An All-Digital Successive Approximation Register Type Fast-Locking Delay-Locked Loop

A delay-locked loop and successive approximation technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems of limited application, harmonic locking deadlock, and excessive locking time, so as to reduce the number of search cycles and avoid harmonics. Wave lock, the effect of eliminating the influence of the crossover ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

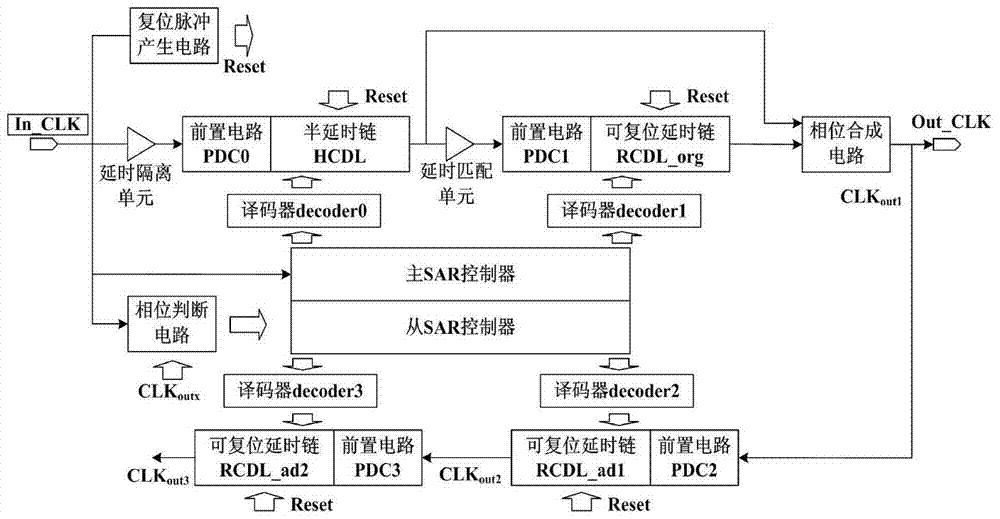

[0028] figure 1 It is a block diagram of an all-digital successive approximation register-type fast-lock delay-locked loop system. The working process of the system can be divided into two steps: 2-bit fast successive approximation register search and phase synthesis, in which 2-bit search is used to complete phase locking, and phase synthesis is used to ensure that a 50% duty cycle clock signal is output after locking. Its working process is as follows: the clock signal passes through a set of half digital-controlled delay chains (Half Digital-ControlledDelayLine, HCDL) and 3 sets of resettable delay chains in sequence in the system, in which RCDL_org, RCDL_ad1, and RCDL_ad2 respectively provide one output signal as the phase Judging the feedback clock of the circuit; at the same time, the clock signal passes through the reset pulse generating circuit to reset the RCDL periodically, and clear the residual signal of the previous cycle in the RCDL. Since the system divider rat...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap