Board level circuit testing model automatic generation method

A board-level circuit, automatic generation technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems affecting the accuracy of fault isolation rate, large workload, high error rate, etc., to save manpower and Time spent, reduced number of cross-connections, easy to observe the effect of analysis

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

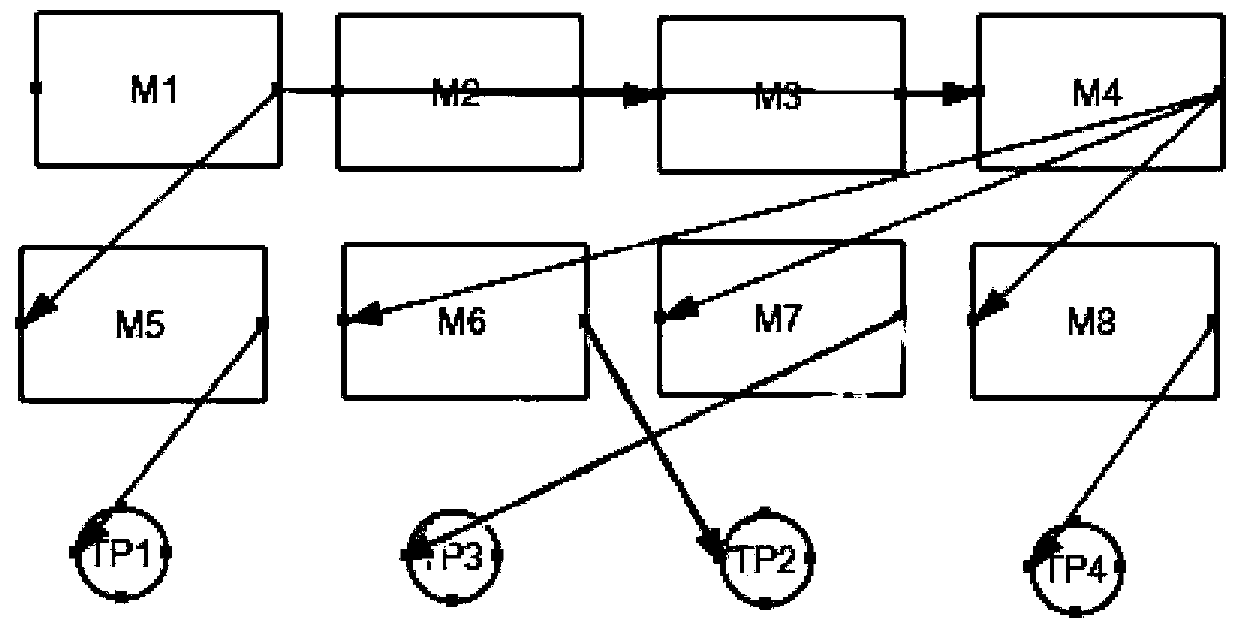

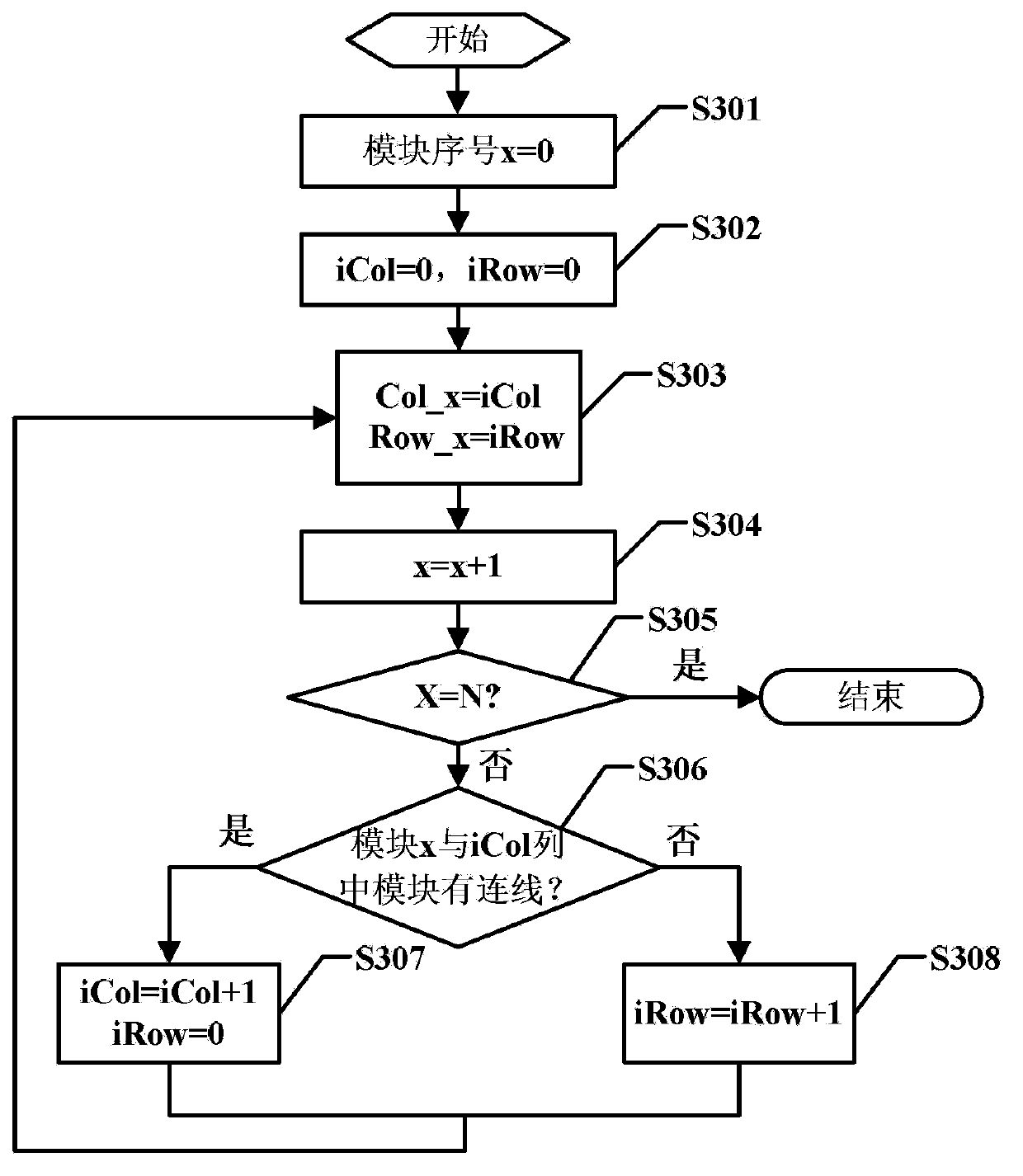

[0050] The method for automatically generating a testable model of a board-level circuit of the present invention comprises the following steps:

[0051] Step 1: Obtain board-level circuit information;

[0052] A board-level circuit consists of multiple board connections. Each circuit board can contain multiple failure modes, and each failure mode is defined as a failure module of the circuit board. The board-level circuit testability model is composed of modules and their connection methods, and the modules include fault modules and measurement point modules. The information required for the generation of the board-level circuit testability model includes the information of each layer of circuit boards, the fault attributes of the faulty modules contained in each layer of circuit boards, the test attributes of the measurement point modules, and the directed propagation relationship between faulty modules, etc. The failure attributes of the failure module include module name...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com