Method for manufacturing TSV seed layer with fine pitch and high depth-to-width ratio

A manufacturing method and high aspect ratio technology, applied in the field of microelectronics, can solve problems such as sealing the TSV mouth, and achieve the effect of low cost and easy realization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

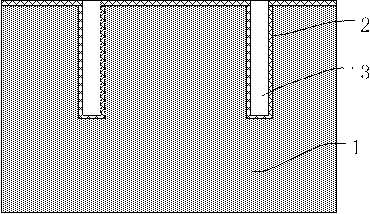

[0025] figure 1 Shown is the wafer substrate that has completed the TSV etching and insulating layer deposition process, where 1 is the substrate and 2 is the barrier layer. The film layer can be silicon dioxide, silicon nitride, silicon oxynitride, organic polymer materials etc. 3 is a TSV hole. There can be zero or more layers of membrane structure 2 covering the sidewall of the deep hole as required.

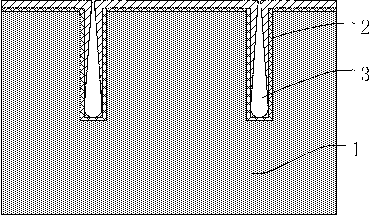

[0026] A metal layer 4 is deposited on the surface of the substrate 1 and in the TSV hole 3 by using a PVD process, such as figure 2 shown. The PVD metal layer includes a barrier layer adhesion layer metal and a seed layer. The material of the barrier layer adhesion layer can be titanium, titanium nitride, tantalum, tantalum nitride, tungsten, tungsten nitride, vanadium, single vanadium, niobium, nitrogen Niobium chloride, etc., and the material of the seed layer is copper.

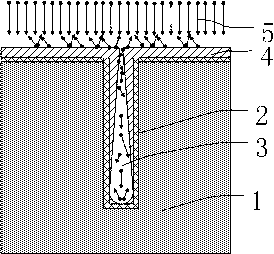

[0027] After the copper is deposited by PVD, the wafer is heated and reflowed in a vacuum or lo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com