Efficient fetch production line supporting synchronous EDAC inspection

An instruction fetch pipeline and pipeline technology, which is applied in concurrent instruction execution, response error generation, and redundant code error detection, etc. Reduce the probability of reading data, eliminate dynamic errors, and enhance the effect of error correction capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

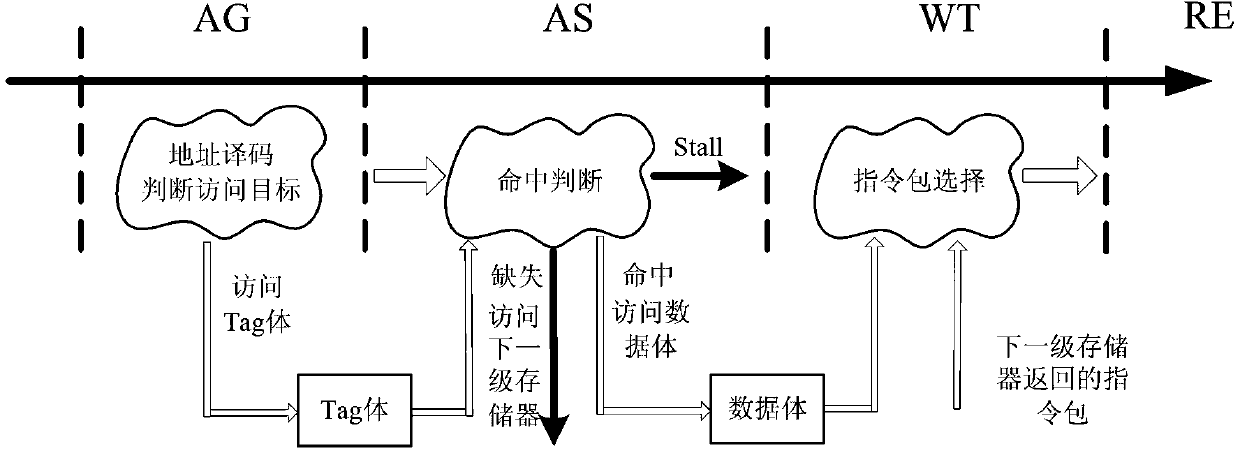

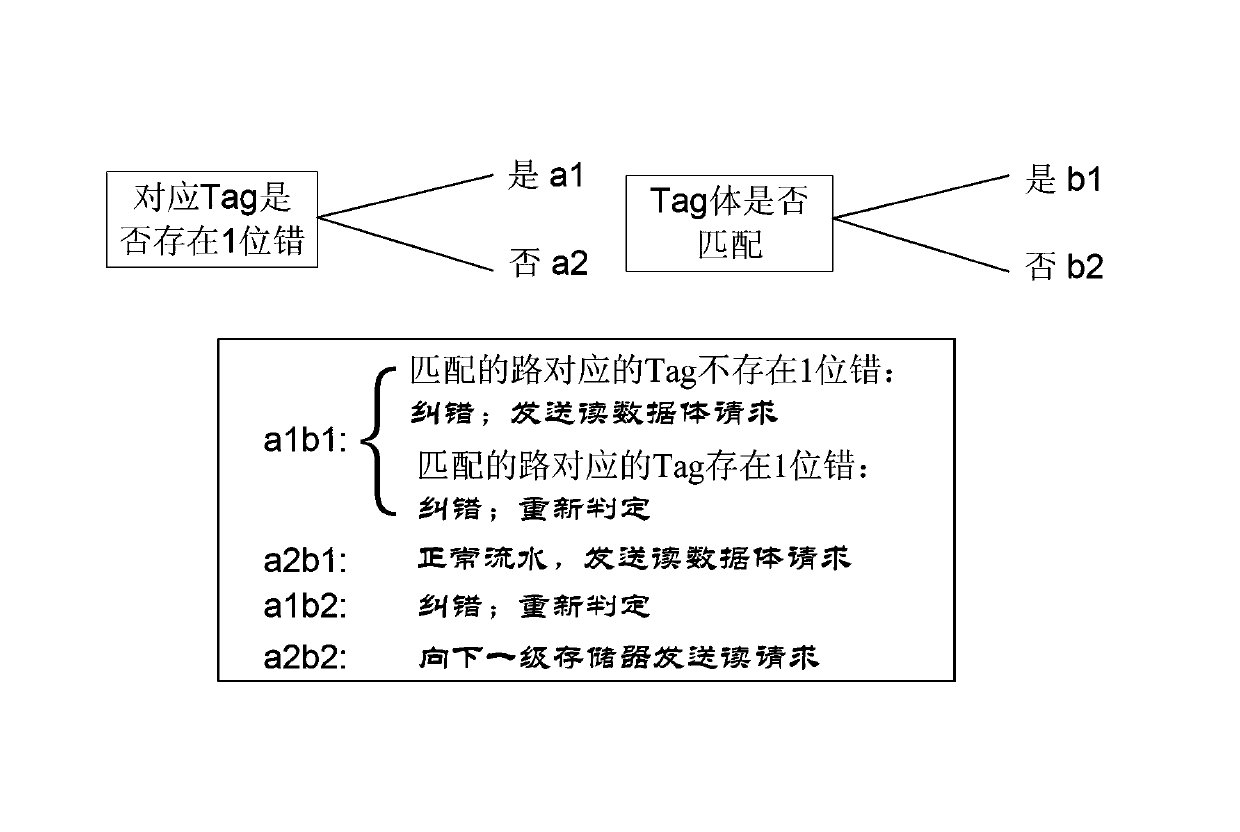

[0057] Such as figure 2 As shown, it is a schematic diagram of an efficient instruction fetch pipeline supporting synchronous EDAC verification in the present invention, and the efficient instruction fetch pipeline in the present invention is actually an instruction fetch method. The flow and logic of the instruction fetching pipeline of the present invention are basically the same as those of the basic instruction fetching pipeline, and are also divided into four stacks, namely: program address generation stack (program Address Generate, AG), program address sending stack (program address send, AS) , Program access ready Wait (WT) stack (program access ready Wait, WT) and program fetch packet receive stack (program fetch packet Receive, RE). Among them, the AG stack is mainly responsible for generating the address of the current in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com