SET/CMOS latch based on negative differential resistance characteristics

A negative differential resistor and latch technology, applied in the field of latches, can solve problems such as limiting SET output swing, increasing circuit transmission delay, and failure to obtain performance, achieving low transmission delay, high operating voltage, and low power consumption. low effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

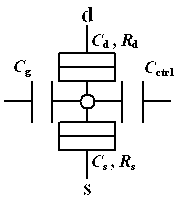

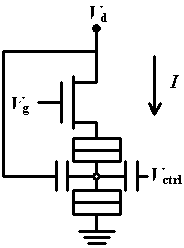

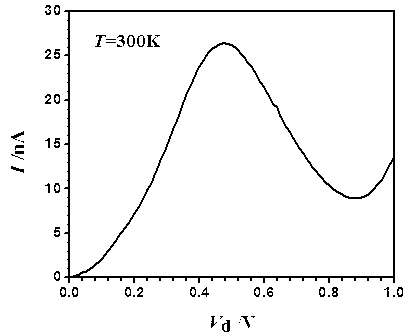

[0022] A single-electron transistor (SET) refers to a device that uses the particle and Coulomb blocking effects of electron charges to control the transfer of a single or a few electrons. Among them, the structure of a double-gate single-electron transistor is as follows figure 1 shown. The double-gate single-electron transistor is composed of two tunnel junctions connected in series through the Coulomb island, and the external bias voltage is capacitively coupled to the Coulomb island to control the tunneling current of the device; the electron tunneling is controlled by the bias voltage, The single-electron transistor has a unique Coulomb blocking oscillation characteristic, that is, as the gate voltage increases, the leakage current of the transistor has a periodic change. Unlike CMOS, single-electron transistors operate at higher drain-source voltages V ds will not enter the saturation state., with V ds The increase of the Coulomb blockage will disappear; therefore, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com