Multi-layer co-sintered lamination stackable chip resistor and manufacturing method thereof

A chip resistor, stacking technology, used in resistor manufacturing, resistors, trimmer resistors, etc., can solve the problems of efficient use, complicated locking and multi-layer co-firing, saving time and eliminating stacking procedures. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

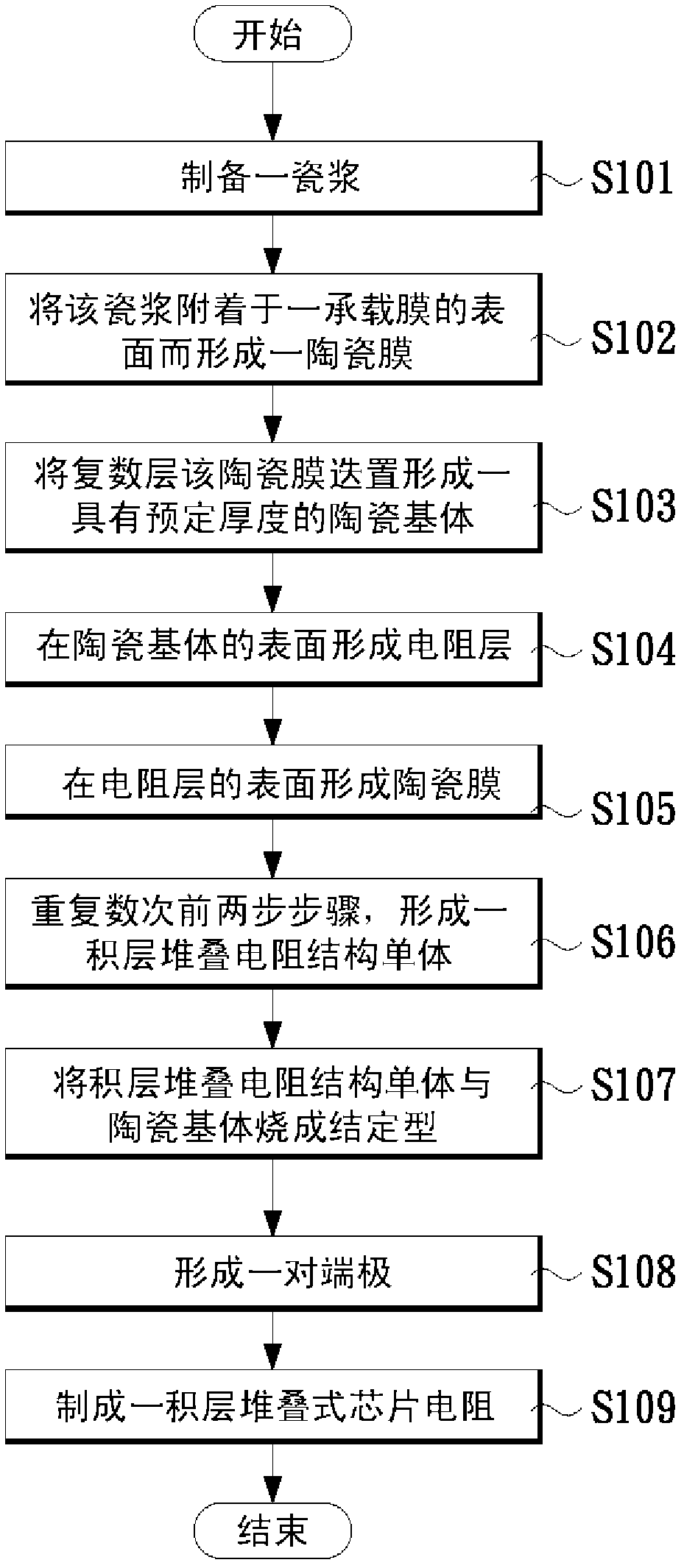

[0055] The multilayer co-fired multilayer stacked chip resistor and its manufacturing method provided by the present invention realize a multilayer stacked chip resistor structure by the multilayer cofiring technology.

[0056] The technical means adopted by the present invention to solve the problems of the known technologies is to firstly prepare a porcelain slurry including a solvent, a binder and a dispersant, and attach the porcelain slurry to the surface of a carrier film to form a ceramic film, and then A plurality of layers of the ceramic film are laminated to form a ceramic matrix with a predetermined thickness. Then a resistance layer is formed on the surface of the ceramic substrate, the ends of the resistance layer extend in a horizontal direction respectively to form terminal connection ends, and the ceramic film is formed on the surface of the resistance layer.

[0057] repeating the first two steps several times to form a monolithic stacked resistance structure ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com