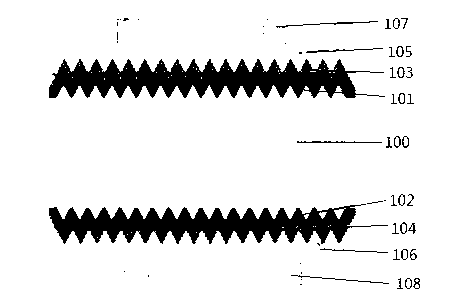

Black heterogeneous crystalline cell and manufacture method thereof

A manufacturing method and technology of crystalline silicon, applied in the direction of final product manufacturing, sustainable manufacturing/processing, circuits, etc., can solve the problems of difficulty in covering amorphous silicon, increased surface area of silicon wafers, etc., to achieve simple and easier control, fragmentation rate Low, low thermal stress effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0036] Embodiment 1, the manufacturing method of black heterogeneous crystalline silicon cell is as follows:

[0037] A. Select an N-type silicon wafer with a resistivity of 1-5ohm.cm; remove the wire damage layer during the silicon wafer cutting process, and the removed thickness is about 5-20um. Depending on the specific silicon wafer cutting process, acid polishing is used to remove the damaged layer (HNO 3 and HF), or alkali polishing process (high concentration of KOH or NaOH); after polishing, the silicon wafer is cleaned to remove surface pollutants, which can be cleaned by RCA process or ozone (O 3 )+HCl / HF for cleaning, and finally dry the silicon wafer in dry nitrogen;

[0038] B. The intrinsic amorphous silicon layer is coated on both sides, and the deposition of the intrinsic amorphous silicon layer adopts the method of plasma enhanced chemical deposition, using SiH 4 and H 2 The mixed gas realizes the coating of amorphous silicon, and the deposition temperatu...

Embodiment 2

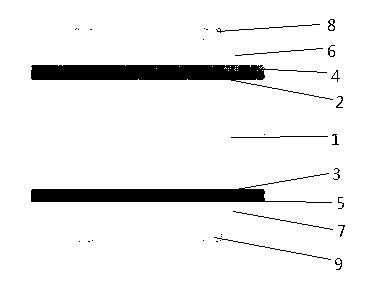

[0043] Embodiment 2, the manufacturing method of the black heterogeneous crystalline silicon battery is the same as that of Embodiment 1, and the specific structure includes the first metal gate line 8, the first polycrystalline boron-doped ZnO thin film 6, the P-type amorphous silicon layer 4, the first intrinsic Amorphous silicon layer 2, a silicon wafer 1, a second intrinsic amorphous silicon layer 3, an N-type amorphous silicon layer 5, a second polycrystalline boron-doped ZnO film 7, and a second metal gate line 9; wherein the intrinsic amorphous The thickness of the silicon layer is 10nm, the thickness of the P-type amorphous silicon layer is 8nm, the thickness of the N-type amorphous silicon layer is 10nm, and the thickness of the positive and negative ZnO conductive films is 1200nm.

Embodiment 3

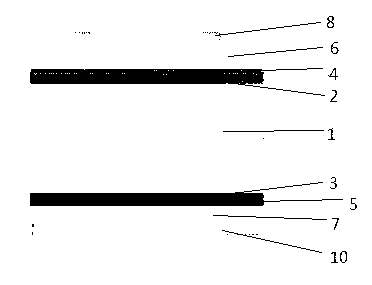

[0044] Embodiment 3, the manufacturing method of the black heterogeneous crystalline silicon battery is the same as that of Embodiment 1, and the specific structure includes the first metal gate line 8, the first polycrystalline boron-doped ZnO thin film 6, the P-type amorphous silicon layer 4, the first intrinsic Amorphous silicon layer 2, a silicon wafer 1, a second intrinsic amorphous silicon layer 3, an N-type amorphous silicon layer 5, a second polycrystalline boron-doped ZnO film 7, and a second metal gate line 9; wherein the intrinsic amorphous The thickness of the silicon layer is 15nm, the thickness of the P-type amorphous silicon layer is 10nm, the thickness of the N-type amorphous silicon layer is 20nm, and the thickness of the positive and negative ZnO conductive films is 2000nm.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com