Flash memory system and managing and collecting methods for flash memory with invalid page messages thereof

A technology of invalid data pages and flash memory, which is applied in memory systems, electrical digital data processing, memory architecture access/allocation, etc., can solve the problem of not being able to use it as a basis for judging the validity of said pages, reducing memory recovery efficiency, and consuming a considerable amount of memory space And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

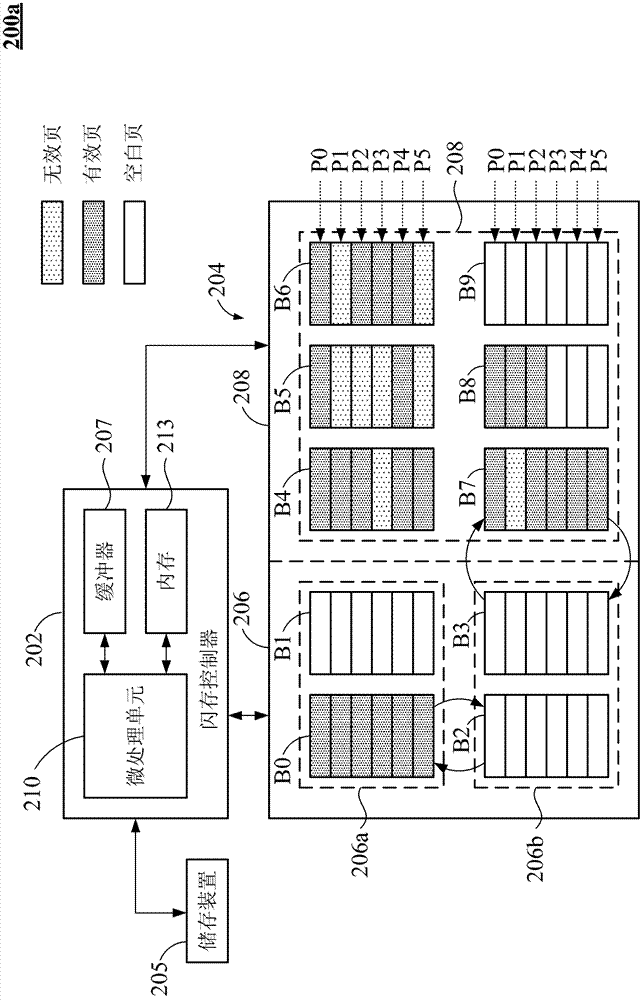

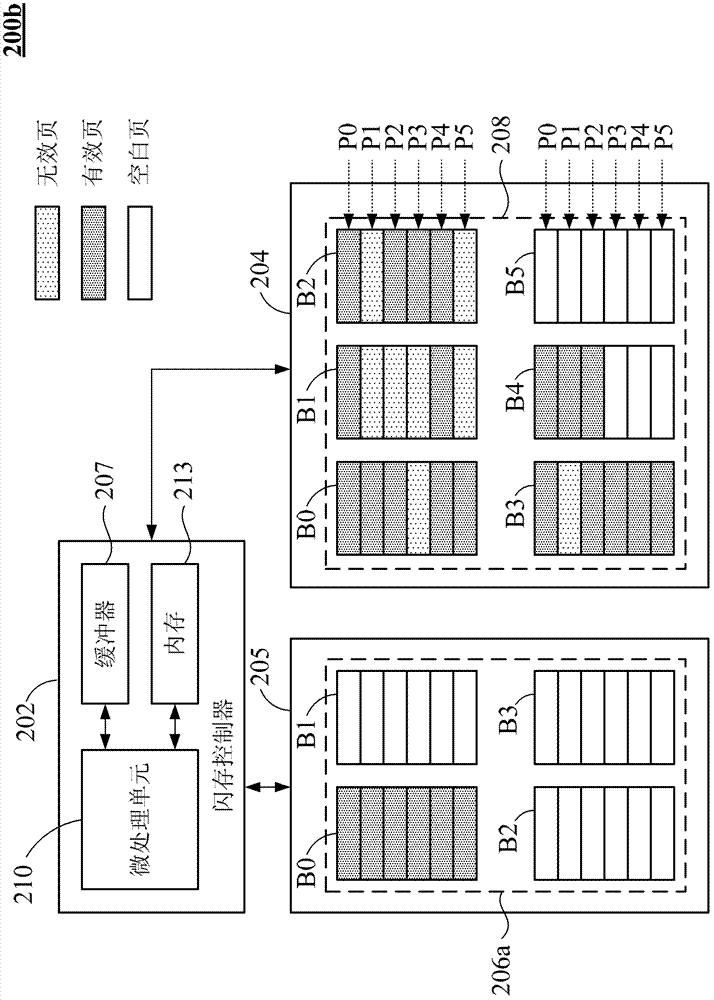

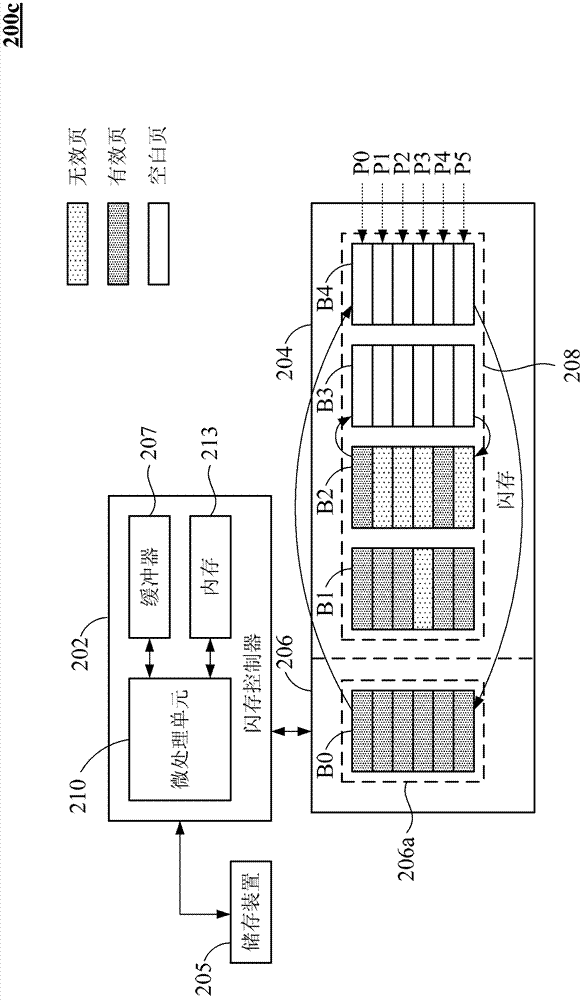

[0021] attached Figure 1A Shown is a block diagram of a management system 200a for invalid data page information of the flash memory in the first embodiment of the present invention. The management system 200a includes a flash memory controller (flash memory controller) 202, a flash memory (flash memory) 204 connected to the flash memory controller 202, and a storage device 205 connected to the flash memory controller 202. The flash memory controller 202 includes a micro processing unit (micro processing unit, MPU) 210, and the buffer 207 and memory 213 connected to the micro-processing unit 210. The management system 200a and method for invalid data page information of flash memory of the present invention are applicable to single-level storage cell (SLC), multi-level storage cell (MLC), triple-level storage cell (triple-level cell, TLC) flash memory and any type of flash memory.

[0022] The flash memory 204 includes a reserved area 206 and a data area 208 , and the reserv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com