Semiconductor packaging structure and module thereof

A packaging structure and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of limited chip support, reduced chip function and reliability, chip stress cracking, etc., to avoid coating The effect of uneven glue, improving the quality of chip packaging, and preventing the problem of chip stress cracking

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be described in detail below in conjunction with specific embodiments shown in the accompanying drawings. However, these embodiments do not limit the present invention, and any structural, method, or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

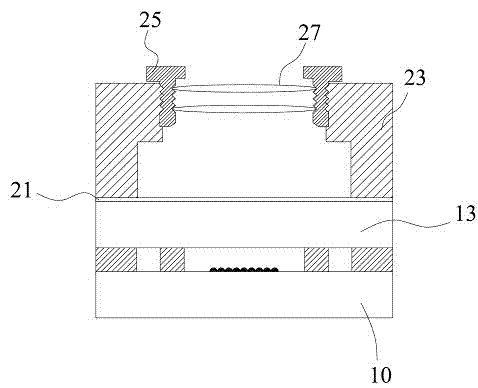

[0027] like image 3 As shown, the semiconductor module according to an embodiment of the present invention includes a semiconductor package structure, a lens assembly, and a filter layer 21 arranged between the semiconductor package structure and the lens assembly, wherein the lens assembly includes A lens container 23 , a lens bracket 25 disposed in the lens container 23 , and at least one lens 27 fixedly arranged by the lens bracket 25 .

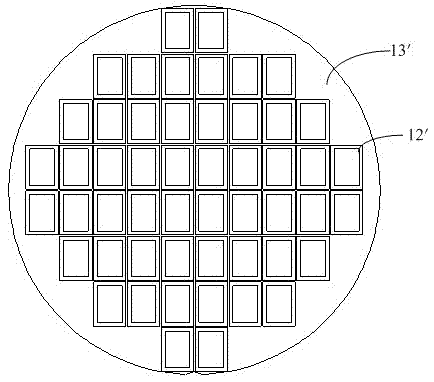

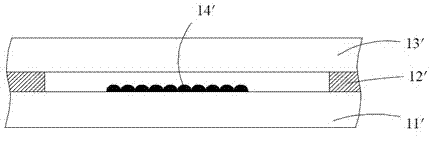

[0028] like Figure 4 As shown, in a preferred embodiment of the present invention, the packaging structure includes a chip 10 and a substrate 13, because Wafer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com