Test structure and test method for negative bias temperature instability of semiconductor device

A technology of instability and test structure, applied in the field of test structure of semiconductor device negative bias temperature instability, can solve problems such as the difficulty of applying the instantaneous test method and the inability of the source measurement unit to test the use of the machine, so as to avoid recovery. effect, the effect of improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

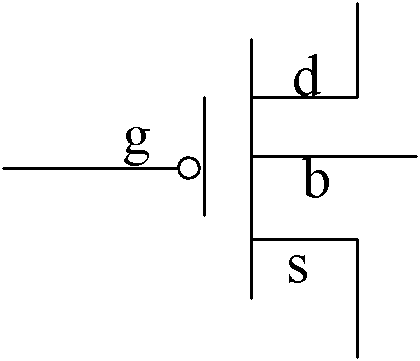

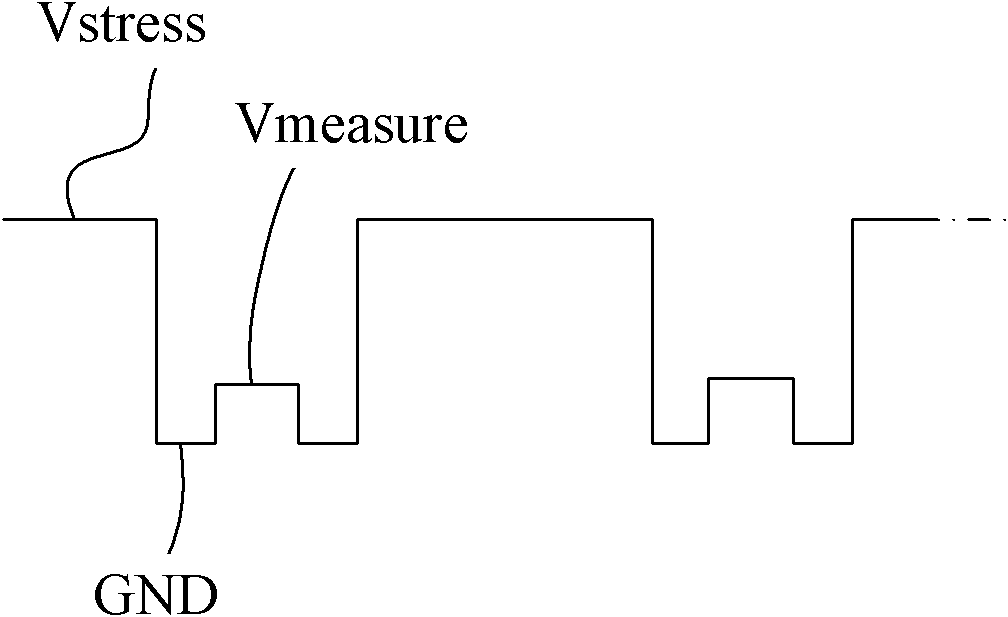

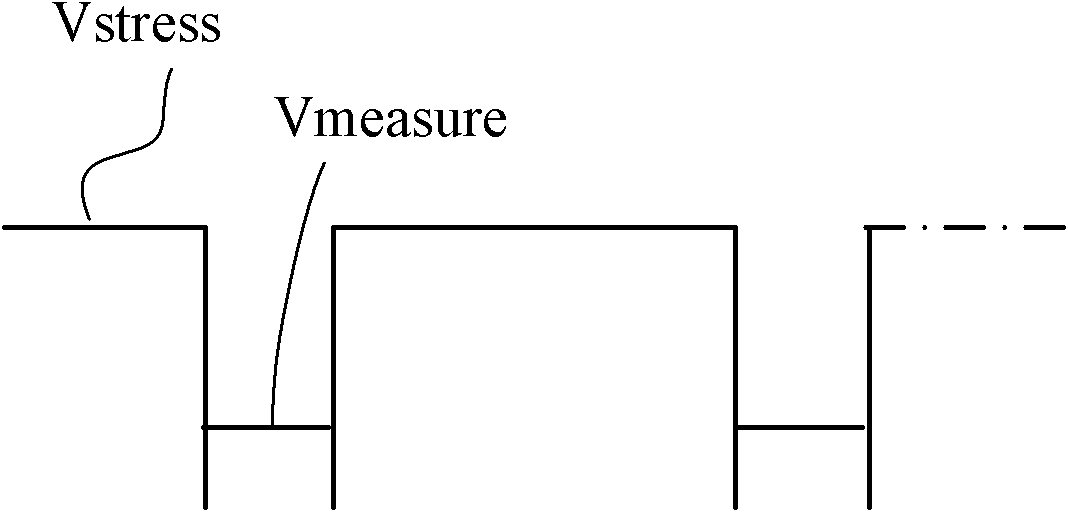

[0032] The test structure and test method for the negative bias temperature instability of semiconductor devices proposed by the present invention will be further described in detail below with reference to the accompanying drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in very simplified form and use imprecise ratios, which are only used for the purpose of conveniently and clearly assisting in describing the embodiments of the present invention.

[0033] The core idea of the present invention is to provide a semiconductor device negative bias temperature instability test structure, the structure includes a bias output device, the voltage of the bias output device on the grid is negatively biased by the stress During the transition from the voltage to the test voltage or from the test voltage to the stress negative bias, a sustain volt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com