Array substrate, method for manufacturing same and display device comprising same

An array substrate and manufacturing method technology, applied in the display field, can solve problems such as light leakage, affecting normal use, and low panel contrast, and achieve the effects of reducing manufacturing costs, improving product quality, and ensuring moderate deflection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

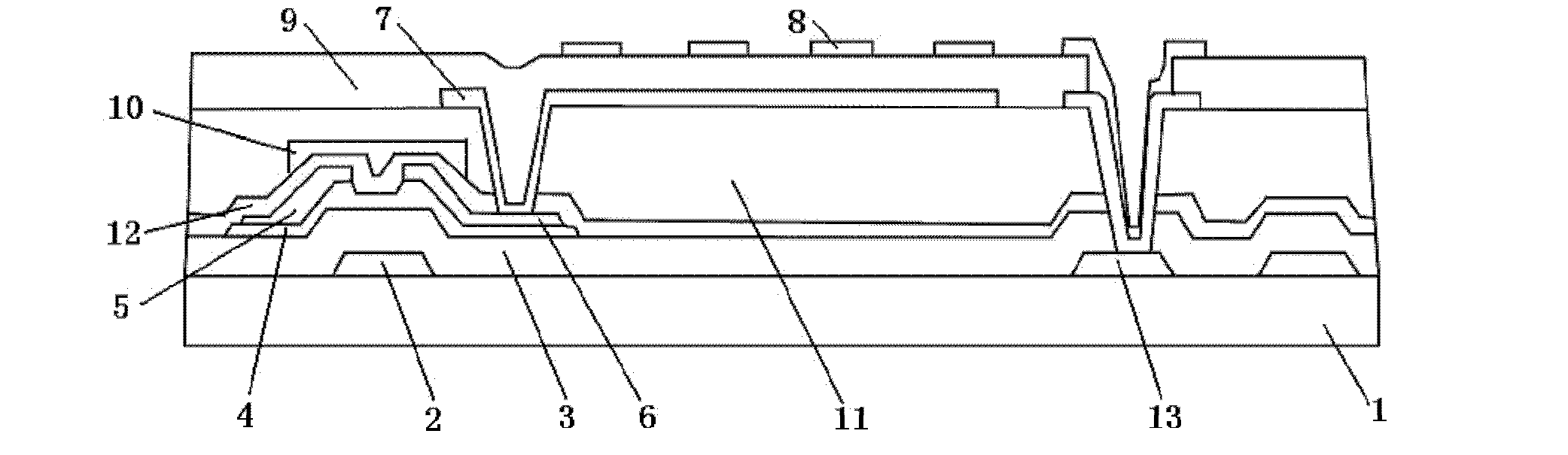

[0030] This embodiment specifically provides an array substrate, which can be applied in the ADS driving mode, such as figure 2 As shown, it includes a gate line and a data line that define a pixel area, the pixel area includes a thin film transistor area and a pixel electrode pattern area, and a gate 2, a gate insulating layer 3, an active layer are formed in the thin film transistor area 4. The source electrode 5, the drain electrode 6 and the passivation layer 9; the gate insulating layer 3, the pixel electrode 7, the passivation layer 9 and the common electrode 8 are formed in the pattern area of the pixel electrode, wherein the common electrode The electrode 8 and the pixel electrode 7 constitute a multi-dimensional electric field; the protective layer 12 can be optionally covered above the gate insulating layer 3 and the source / drain and then a black matrix layer 10 is formed above the source / drain and the TFT channel, or The black matrix layer 10 is formed directly a...

Embodiment 2

[0053] This embodiment provides another array substrate. Since the above-mentioned Embodiment 1 has been described in detail, some repetitive content will be omitted in this embodiment, and only the differences will be described in detail here.

[0054] The array substrate provided by this embodiment can be applied in the ADS driving mode, such as Figure 4 As shown, it includes a gate line and a data line that define a pixel area, the pixel area includes a thin film transistor area and a pixel electrode pattern area, and a gate 2, a gate insulating layer 3, an active layer are formed in the thin film transistor area 4. The source electrode 5, the drain electrode 6 and the passivation layer 9; the gate insulating layer 3, the pixel electrode 7, the passivation layer 9 and the common electrode 8 are formed in the pattern area of the pixel electrode, wherein the common electrode The electrode 8 and the pixel electrode 7 constitute a multi-dimensional electric field.

[0055] ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| optical density | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com