Laterally diffused metal oxide semiconductor (LDMOS) transistor, layout method and manufacture method

A layout method and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as inability to turn on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

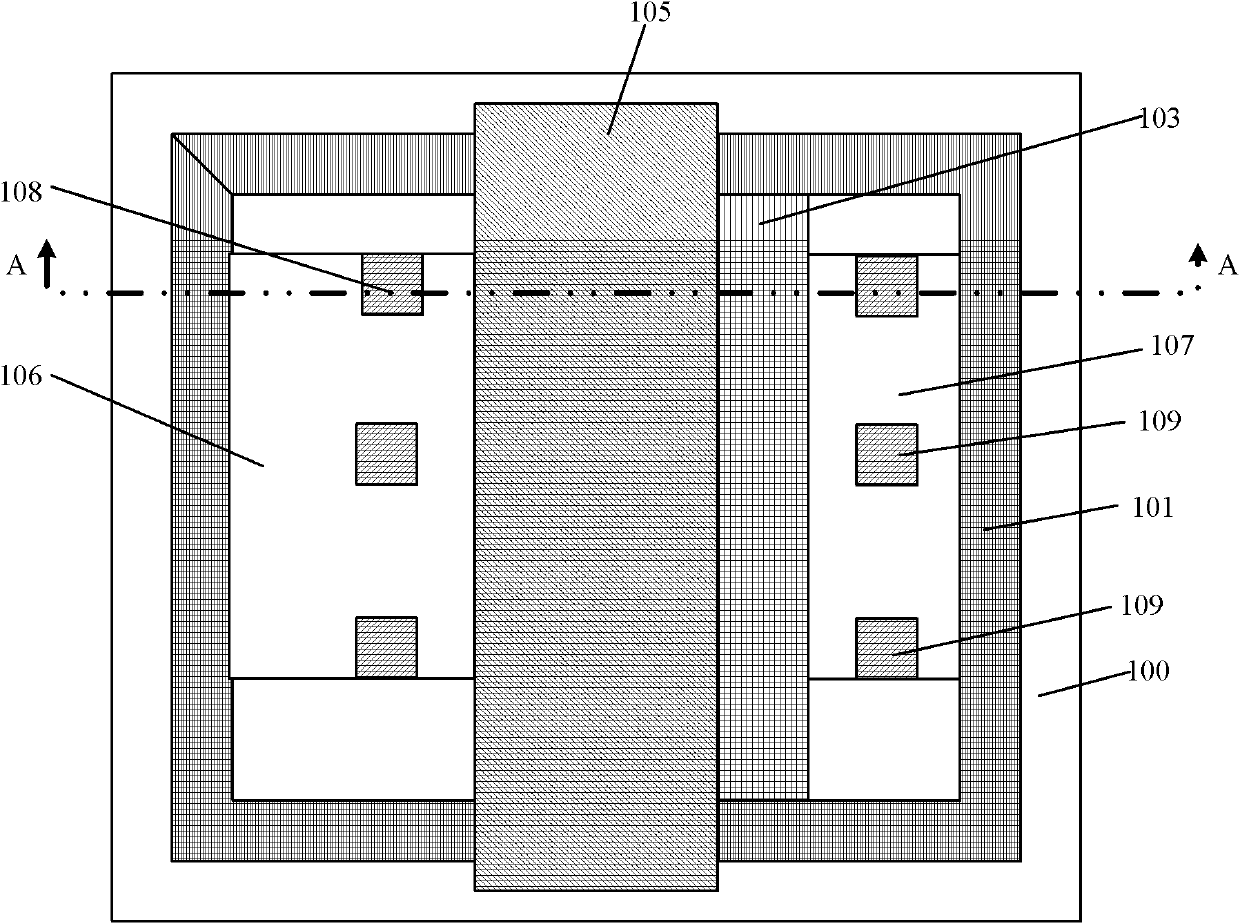

[0050] When the existing LDMOS transistor is applied to ESD protection, the drain region is connected to the IO pad of the element to be protected, and the drain region receives the input voltage signal of the IO pad. Such as figure 2 As shown, when the input voltage signal received by the drain region 107 is less than the maintenance voltage of the LDMOS transistor, the LDMOS transistor is in an off state; when the input voltage signal received by the drain region 107 is greater than or equal to the maintenance voltage of the LDMOS transistor, that is Electrostatic discharge occurs, so that the LDMOS transistor is turned on, thereby forming a conductive channel in the semiconductor substrate 100 below the gate 105, and the electrostatic discharge current passes through the second doped well 112, the conductive channel, and the first doped well 112 from the drain region 107. The heterowell 111 reaches the source region 106 and is grounded through the conductive plug 108 in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com