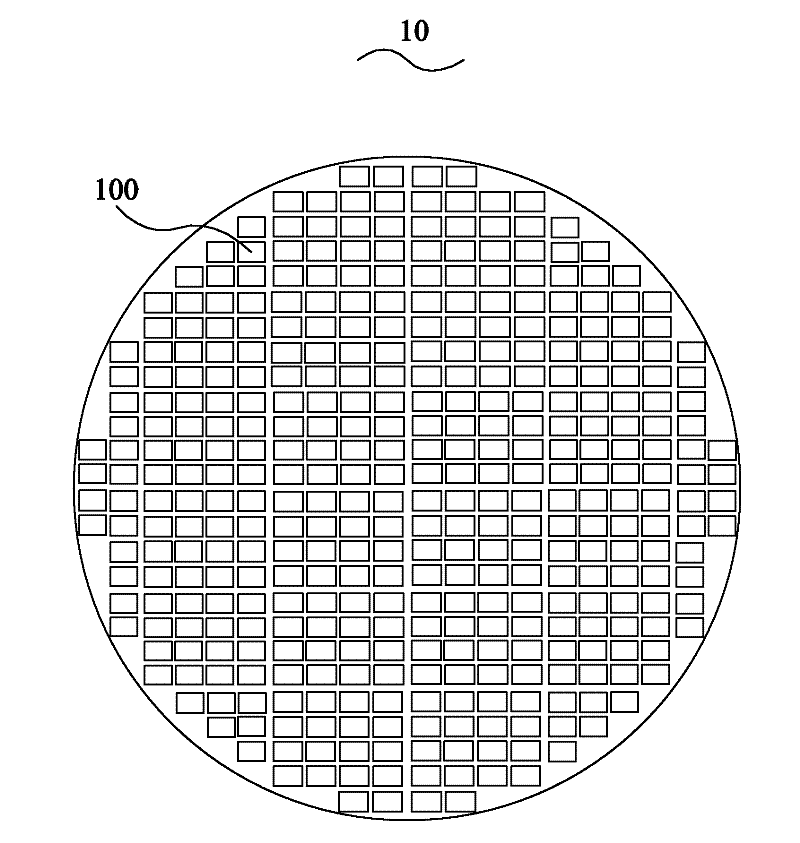

Wafer-level packaging method

A wafer-level packaging and chip technology, which is applied to the formation of wafer-level chip-scale packaging, can solve the problems of short circuit of solder bumps, easy dripping between solders, affecting product reliability, etc., to meet the requirements of fine pitch and improve function The effect of the number of output ports

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

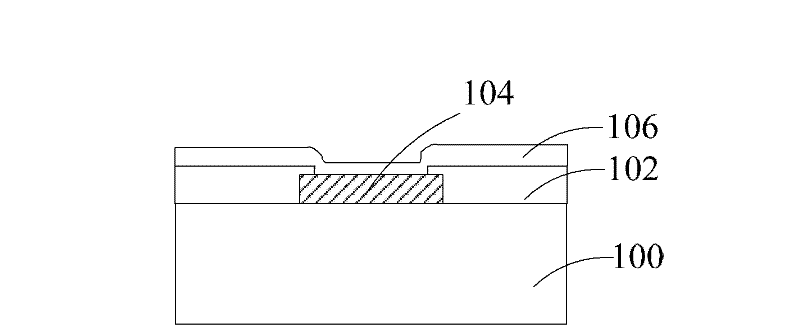

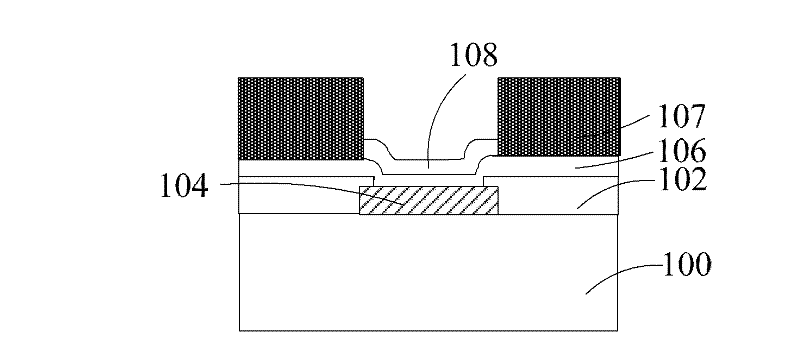

[0031] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0032] figure 2 It is a flow chart of a specific embodiment of a wafer-level packaging method formed by the present invention, including steps:

[0033] S101, sequentially forming a heat-resistant metal layer and a metal wetting layer on the chip pad and the passivation layer;

[0034] S102, forming a photoresist on the metal wetting layer, the photoresist is provided with an opening to expose the metal wetting layer above the chip pad;

[0035] S103, forming a connection layer on the metal wetting layer in the opening;

[0036] S104, removing the photoresist;

[0037] S105, etching the heat-resistant metal layer and the metal wetting layer on the passivation layer until the passivation layer is exposed;

[0038] S106, forming a protective glue layer on the chip, the protective glue covering the connection layer;

[0039] S107, expos...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com