Random sampling analog circuit compressed sensing measurement and signal reconstruction method

A technology of analog circuit and signal reconstruction, applied in analog circuit testing, electronic circuit testing, etc., can solve problems such as low test efficiency, difficulty in modeling fault diagnosis equations, and complex and diverse fault conditions in analog circuits.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

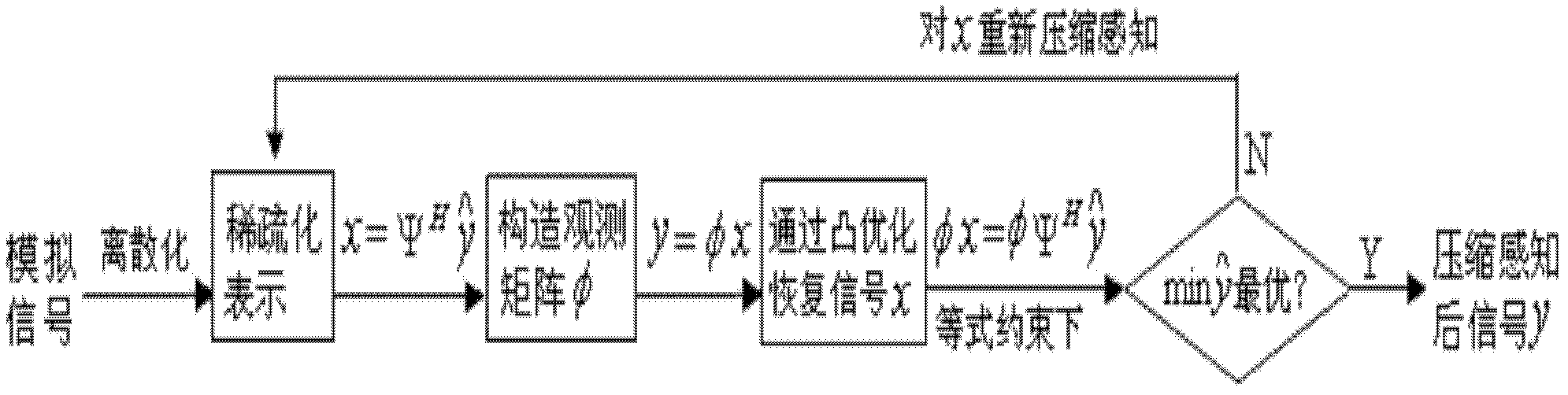

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will now be further described with reference to the accompanying drawings and examples. The effect of the solution of the present invention is described below with a specific example.

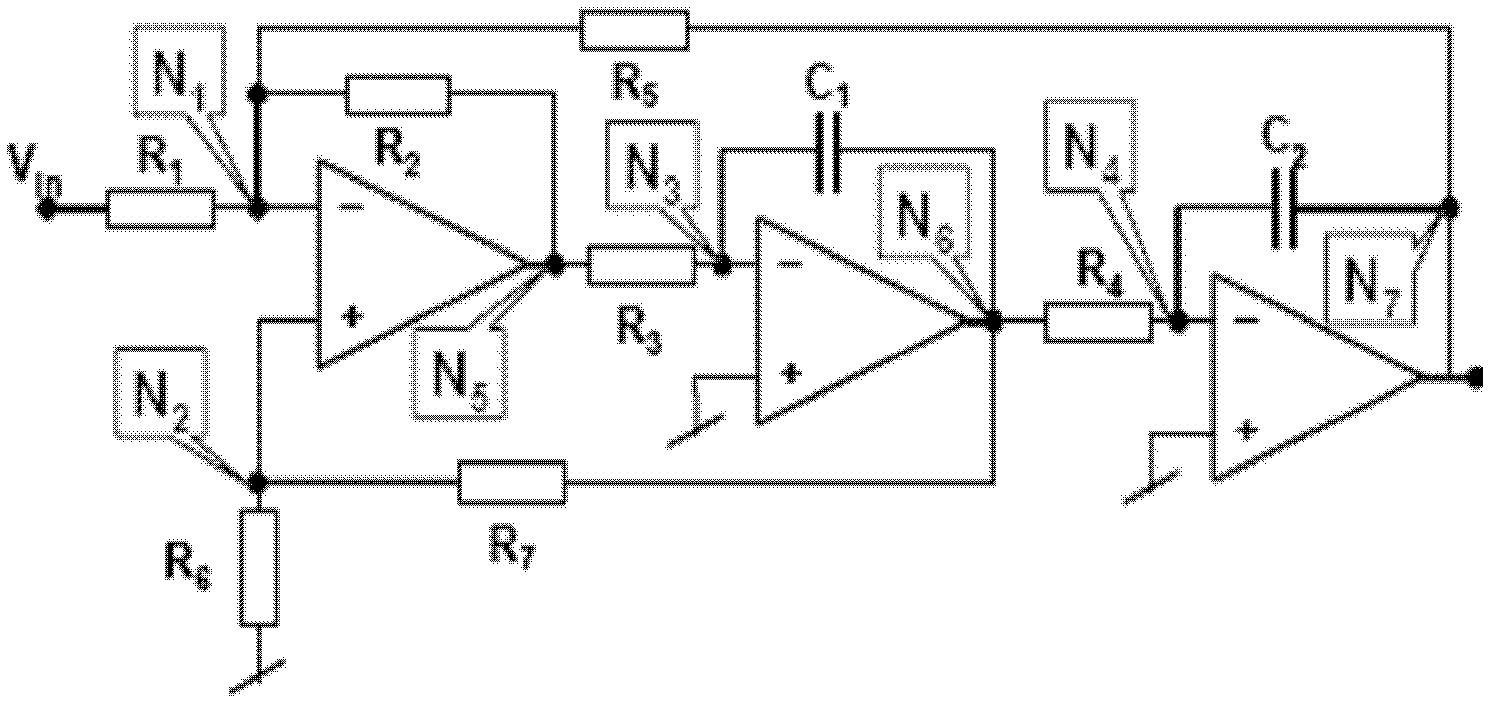

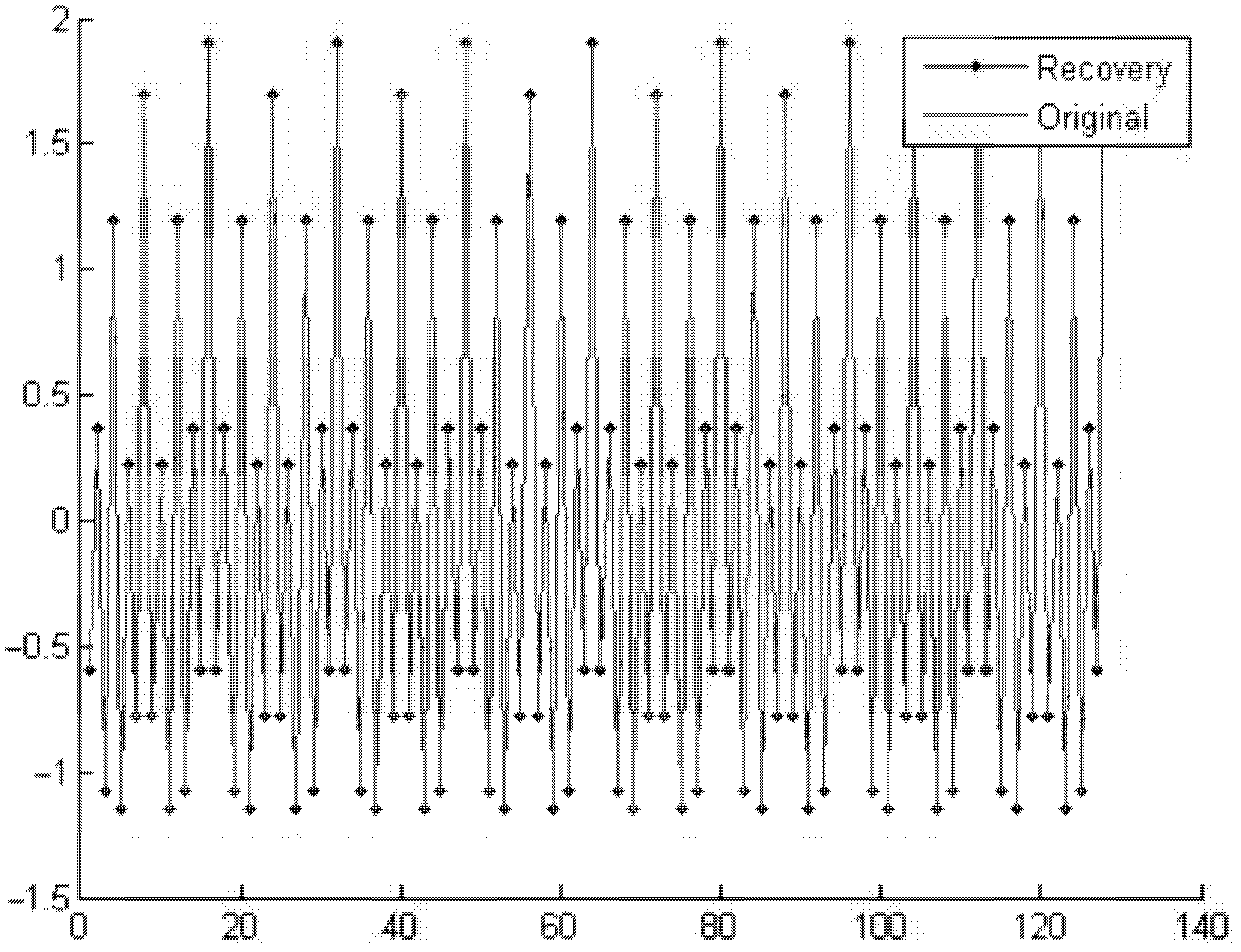

[0044] Test example circuits such as figure 2 As shown in the figure, 7 test nodes are arbitrarily selected to set sensors at the output node of the analog circuit to construct a distributed test network. The following only takes the 7th node sensor to randomly sample the fault response signal as an example to illustrate its compression measurement and signal reconstruction effects.

[0045] The sparse signal generation process that satisfies the K-sparseness in the frequency domain is defined as follows:

[0046] 1. Discretization processing and sparse representation of the response signal:

[0047] If the seventh node of the analog circuit outputs a one-dimensional time domain continuous signal x(t), it is shown in formula 5.

[0048] x(t)=0.3cos(2πf 1 T s t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com