Method and device for testing data valid window of double data rate-3 (DDR3)

A data efficient and data technology, applied in electrical digital data processing, static memory, instruments, etc., can solve the problems of multiple fpga logic resources, difficult to meet engineering timing, difficult layout and wiring, etc., to save logic resources and reduce the difficulty of layout and wiring. , Guarantee the effect of timing requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

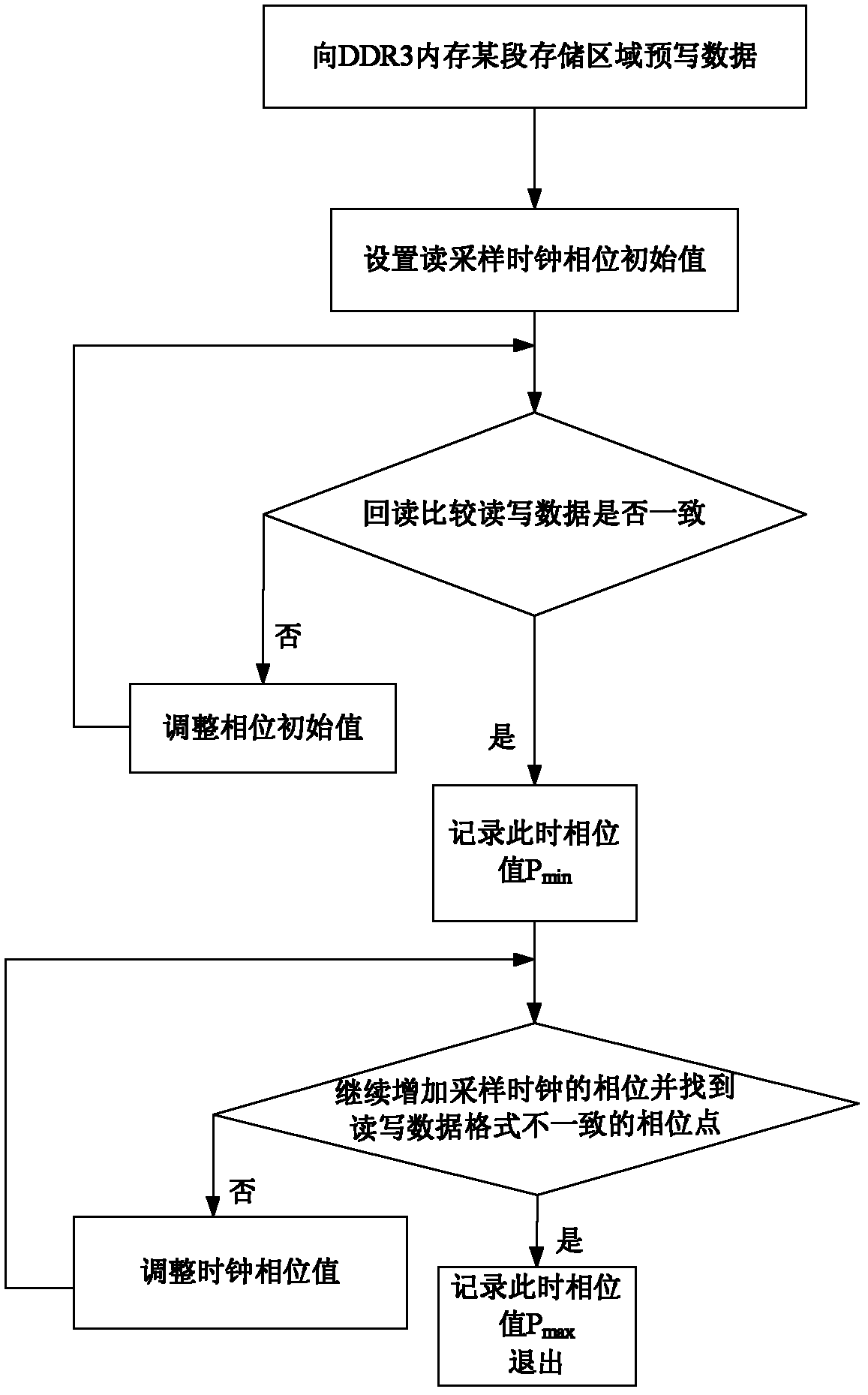

[0021] Such as figure 1 As shown, the method of testing the effective window of DDR3 data does not occupy any logic resources of the fpga. It can directly test and calculate the effective window range of DDR3 data, and then set the phase of the read data sampling clock according to the window size. The concrete process of the method for the effective window of described test DDR3 data is as follows: the initial phase that reads the data sampling clock is fixed as 0 °, a section of regular data is prewritten to a certain section storage space of DDR3 internal memory, then reads back and compares whether the data is consistent with the written If the format of the input data is consistent, increase the phase of the read data sampling clock by one step. Taking a 200MHz clock as an example, the step of the phase-locked loop is 9°, and the phase of the read data sampling clock is fixed at 9°. Then read back and compare whether the data format is consistent with the written data for...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com