Apparatus for testing PCIe bus bandwidth and method thereof

A bandwidth and message data technology, applied in digital transmission systems, electrical components, transmission systems, etc., to solve problems such as limited CPU computing power, inability to measure the reliability and stability of PCIe interfaces, and data traffic that cannot reach the maximum bandwidth. , to achieve the effect of saving address calculation time, high accuracy and reducing use cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

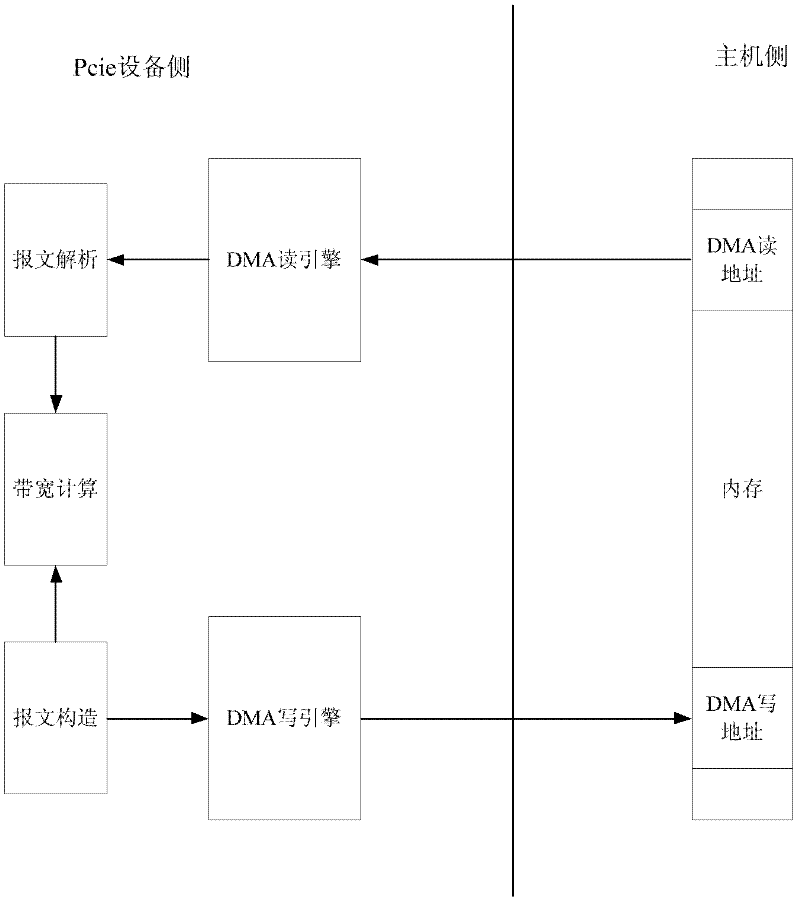

[0018] Such as figure 1 As shown, the device for testing the PCIe bus bandwidth includes: a memory located in the host device; a message construction module, a DMA write engine module, a DMA read engine module, a message analysis module, and a bandwidth calculation module located in the PCIe device ;

[0019] The device for testing the PCIe bus bandwidth constructs a message on the message construction module of the PCIe device, and then uploads the structured message to the DMA of the host memory through the DMA write engine module write address, the DMA read engine module reads data from the host memory address through the DMA read address of the host memory and transmits the read data to the message analysis module, and the message analysis The module submits the length information of the message data to the bandwidth calculation module; finally, the bandwidth calculation module calculates the bandwidth of the message according to the length information of the obtained mes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com