Preparation method of silicon-based gallium arsenide material structure applied to nmos

A silicon-based gallium arsenide, material structure technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as inability to extend, and achieve the effects of improving quality, reducing defects, and optimizing growth rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] see Figure 1 to Figure 6 , the present invention provides a method for preparing a silicon-based gallium arsenide material structure applied to nMOS, comprising the following steps:

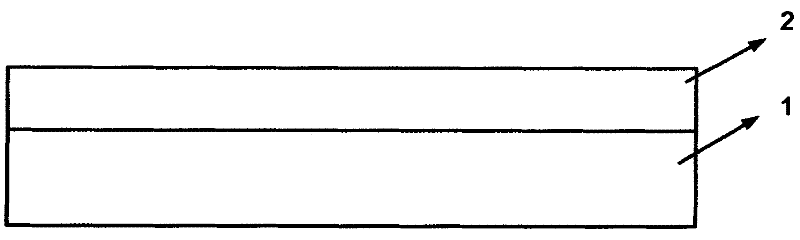

[0031] Step 1: growing a silicon dioxide layer 2 on a silicon substrate 1, the silicon substrate 1 is high-resistance (001) silicon with a p-type resistivity greater than 2000Ωcm, and the thickness of the silicon dioxide layer 2 is 500nm-1000nm ;

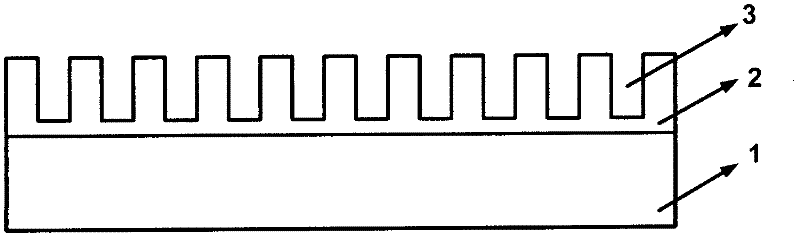

[0032] Step 2: using traditional photolithography and RIE methods to etch a plurality of trenches 3 on the silicon dioxide layer 2 along the direction of the silicon substrate 1, and the width of the trenches 3 is 200-300nm;

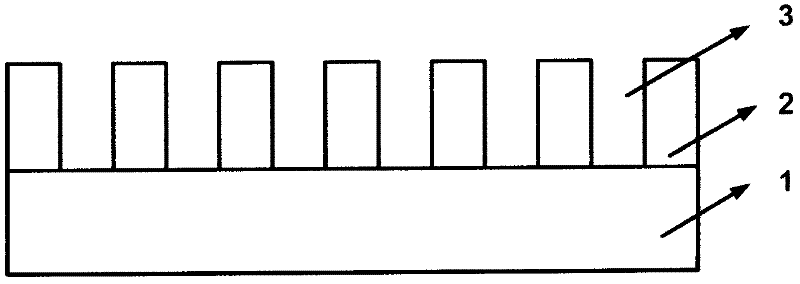

[0033] Step 3: Use piranha and SC respectively 2 , HF and deionized water cleaning, remove the remaining silicon dioxide layer 2 at the bottom of the trench 3, and expose the silicon substrate 1, the remaining silicon dioxide layer 2 in the trench is to protect the silicon substrate from being damaged by etching ;

...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com